どうも、さわざわです。

今回は短チャネル効果について触れていこうと思うよ。半導体って小さく作ることで繁栄してきたっていっても過言じゃないと思うけど、微細化を押しとめている要素の一つがこの短チャネル効果だね。デバイスの領域で触れていくと年を越してしまうくらい濃厚な内容なので、今回はさっぱり基礎的な話でのみ語ろうと思うよ。アナログ回路設計目線での微細デバイスの影響は、別途記事にしようと思ってるよ。みんなも勉強していってねい。

この記事を読めば、短チャネル効果の基礎概要とその対策方法(逆短チャネル効果など)についてわかります。

Contents

半導体デバイスにおける微細化の凄み

半導体界隈には有名な法則として、ムーアの法則ってのとデナード則ってのがあるよ。

ムーアの法則っていうのはトランジスタの集積密度が18~24か月ごとに倍になるってことだよ。つまりは半導体デバイスが微細化されていく速度を予言しているようなものだね。これが近年まで大外ししていないのがすごいところ。

デナード則はスケーリング則って言われるけど、電界を一定にしたまま寸法を縮小してくと、デバイス寸法と電源電圧が1/K倍に比例縮小していくものだよ。

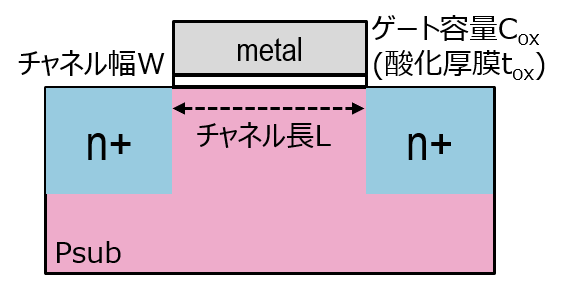

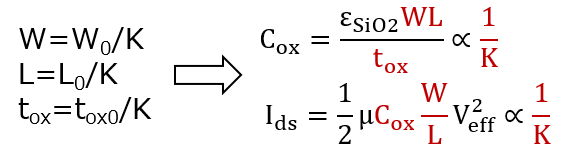

具体的にどう変わっていくか説明するね。寸法が1/K倍に小さくなると、当然チャネル幅Wとチャネル長Lも1/K倍されるね。あとは酸化膜厚も1/K倍されるから、ゲート容量Cox自体は以下のように1/K倍されることになるね(単位面積で見たらK倍だけどね)。そうなるとドレイン電流Idsも、アスペクト比は変わらなくてもCoxが1/K倍されるから1/K倍になるよね。

この結果、まず回路伝達速度が速くなる。というのも時定数は以下のように表せて、1/K倍で微細化に伴い速度面で性能が良くなることがわかる。

もう一つは消費電力。これは単純に以下のように表せて、なんと1/K2に抑えることができる。

そしてもちろんトランジスタの面積は1/K2になるわけだから、同じ面積のチップにトランジスタ数をK2倍積めることができるわけで、同じ性能のチップを安く作ったり同じ面積(コスト)のチップをより高性能な処理を持たせて作ったりできるわけなんだ。

ここまで、スケーリング則にのっとって小さくすればいいことづくめなのがわかったかな?しかしながら現状は、小さくすると次にあげるような短チャネル効果をはじめとしたさまざまな弊害が出てきて、理想通りに微細化ができずかなりテクニカルなレベルにまでデバイスは進化を求められているよ。

短チャネル効果って?―閾値電圧の変動―

短チャネル効果って大きく括るといろいろ弊害が挙げられるんだけど、ここでは閾値電圧の変動を触れるよ。

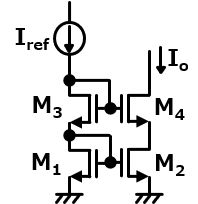

閾値電圧の考え方だけど、nchの場合ゲート電圧をあげていくとチャネル化に空乏層が形成されて、固定電荷が増えてくるよね。ざっくりいうと、この固定電荷があるレベルまで増えていったら(空乏層が伸びていったら)反転層が形成されてnchがオンするって時のゲート電圧が閾値電圧なわけだね。

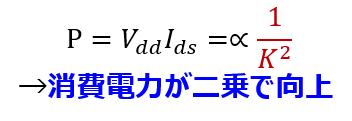

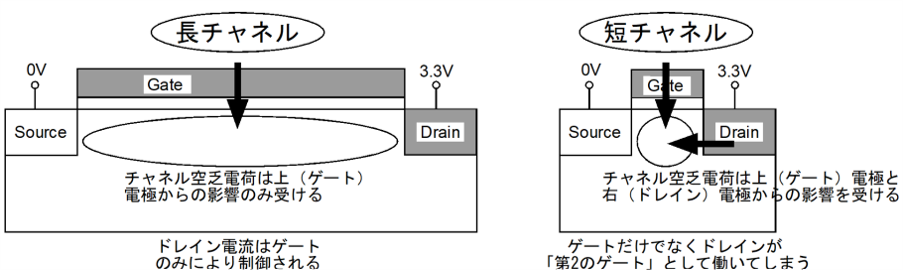

これが以下のように短チャネルになっていくと、ソースやドレインにもソース・ドレインのn+と基板のpでpn接合ができているわけで、その際は必ず空乏層ができてしまうね。んで本来ゲートで作るはずだった固定電荷をソースやドレインの空乏層にいる固定電荷が補ってしまって、実効的にゲートにかける電圧が小さくても反転層が形成されてしまい、閾値電圧が下がって見えてしまうんだ。

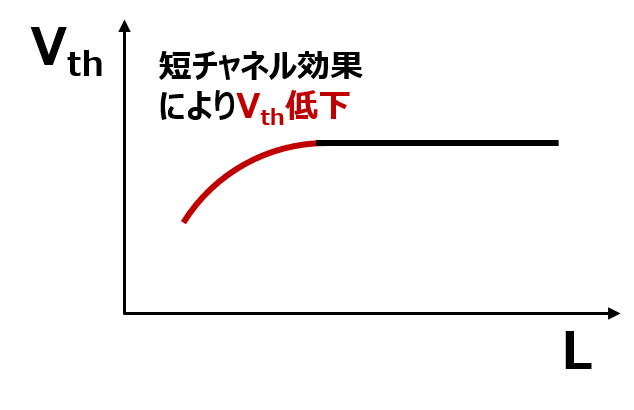

結果として、以下のようにチャネル長を短くしていくと、一定にしたかったVthは減っていってしまう。

DIBL

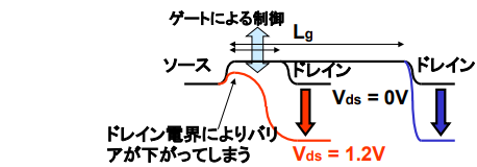

あとはDIBL(ドレイン誘起障壁低下現象)ってのがあって、絵で説明すると以下のようにチャネル長が短いとドレイン電圧印加に伴い、オフ時のソースとドレインを隔てる障壁がつられて下がってしまい、Vthが小さくなる現象だよ。

一個前の説明で考えるならドレイン電圧を印加するとドレイン側で形成されたpn接合の空乏層が伸びてしまい、よりチャネル下にドレイン起因の固定電荷が増えて見えて、Vthが小さくなるってことになるね。

短チャネル効果って?―サブスレッショルドリーク電流の増大―

まずVthが想定より下がってしまうことで、オフ時の電流を理想的には0にしたいけどチョロチョロと流れてしまい、サブスレッショルドリーク電流が増大してしまうよ。

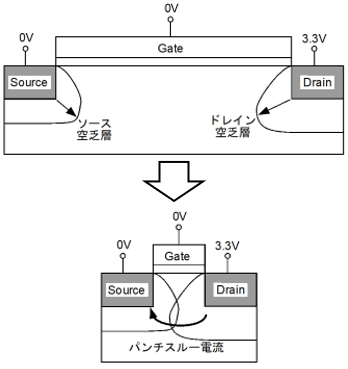

短チャネルデバイスの場合それだけではなくて、以下のようにチャネルより下の位置にソース・ドレインの空乏層がつながってしまい、ゲート制御に依らずリーク経路が形成されてしまうことがあるんだ。この場合は閾値電圧によらずトランジスタはスイッチとして使い物にはならなくなってしまうよね。総括するとソース・ドレインから空乏層を延びることは出来れば抑えたいんだ。

ここまでの基礎デバイスな内容は以下から抑えてみるのがおすすめ。

半導体デバイス入門: その原理と動作のしくみ (新・電子システム工学 TKR-6)

もっと深ーくデバイス特性について学習したい場合はタウアニンがいいと思う。ほんとに幅広く扱ってて、かなり役に立つ。最近第3版が出たけど、中古なら第2版のほうがいいのかも。

短チャネル効果の抑制方法ー逆短チャネル効果ー

いくつかあるので代表的なものをあげていくよ。

まずは単純に基板pchの不純物濃度を上げる方法。ドレインやソースからの空乏層の伸びを抑えたい場合、pnの濃度差を大きくすれば空乏層が短くなるんだね。これでチャネルへの侵入はある程度抑えられる。このデメリットって思いつくかな?

それは、Vthが高くなりすぎることだね。本来スケーリング則にのっとると電源電圧も下げたいわけで、そうすると当然駆動するデバイスのVthも下げないと十分に活用できないよね。そうなるとチャネル部の不純物濃度をあげてVthも大きく上げてしまうというのは得策じゃないね。

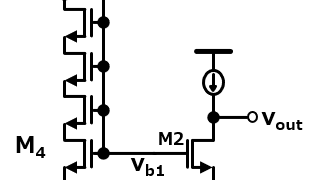

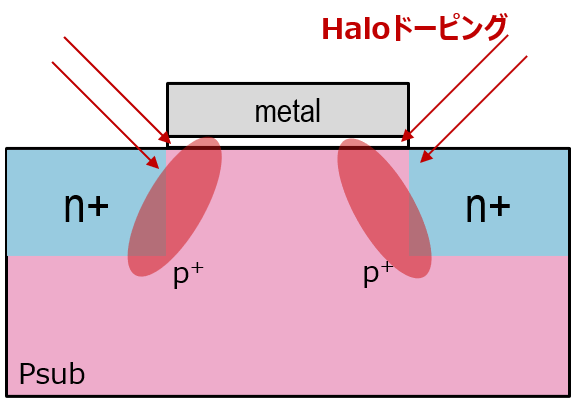

次にあげるのは逆短チャネル効果って呼ばれるもので、これがなかなかよく考えられていてあっぱれって感じ。やり方としては、以下のようにソース・ドレイン部の側近にだけ、p+のドーピングをするんだね。ハロー(後光)ドーピングって呼ばれてるんだけど、これによってまずソース・ドレインからの空乏層の伸びを抑えられる。

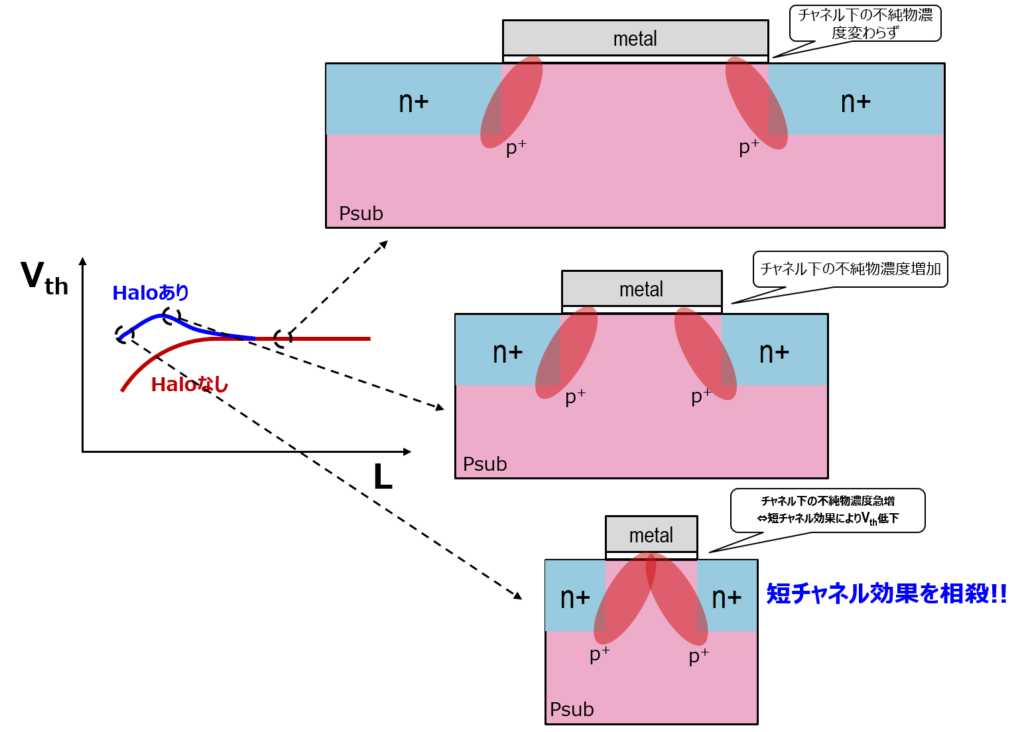

それだけでななくて、長チャネルの場合は、チャネル下の平均的な不純物濃度はPsubの濃度で決まるため、通常のトランジスタと同様に使えるんだけど、短チャネルになって先述したようなVth低下が起こり始めると、以下のようにチャネル下の平均不純物濃度にハロードーピングの効きが強くなってきて、Vthが増加し始める。

つまりは短チャネル効果のVth低下をハロードーピングによってVthを増加することでVth変動をできるだけ相殺させるってのが、逆短チャネル効果になるよ。製造プロセスに工程は増えるけど、これはすでにかなり確立された製造方法だよ。

次回予告ーFDSOIについてー

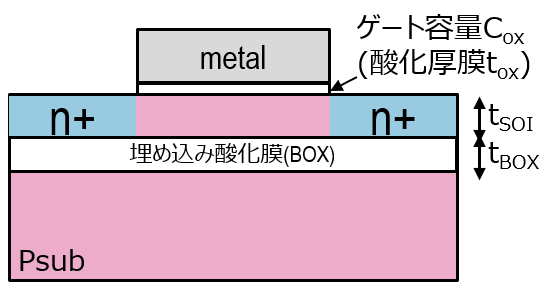

もう一つは次回予告。短チャネル効果を超えて微細化を進めていくうえで、トランジスタっていうデバイス構造そのものが大きく進化してきているよ。その進化の第一歩として、以下のようなFDSOI構造のデバイスがあるよ。こういった構造にすることで従来のバルク構造よりどういった利点があるのかを考えてみてね。

今日はここまで、ほな。

雑談枠

大晦日のRIZIN、めっちゃ面白かったなあ。呼吸することも忘れて泡吹いて倒れてた。Abemaで見てたんだけど、まじで現地まで行ってみることを検討したい。堀口選手、結婚おめでとうございます。

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。