どうも、さわざわです。

今日は位相補償について、ポールスプリットに触れていこうと思うよ。ポールスプリットだけとっても内容がかなり盛りだくさんなので、何回かに分けて記事にしていければと思うよ。安定性を担保したオペアンプを設計するうえで位相補償は非常に重要な知識となってるので、みんなも勉強していってねい。

(ちなみに以下は考え方の一例に過ぎなくて、仕様によってどう位相補償するかの結論は変わってくることに注意してね)

この記事を読めば、ポールスプリットを用いた位相補償について基礎的な理解ができ、伝達関数での計算などより応用的な内容につなげていきます。

ポールスプリットとは?

まずは以前までの記事を先に読んでおくことを強くお勧めするよ!(特にオペアンプの安定性の話)

→ネガティブフィードバックについて

安定性設計におけるポールと位相余裕について

オペアンプの安定性と最適な位相余裕について(おすすめ)

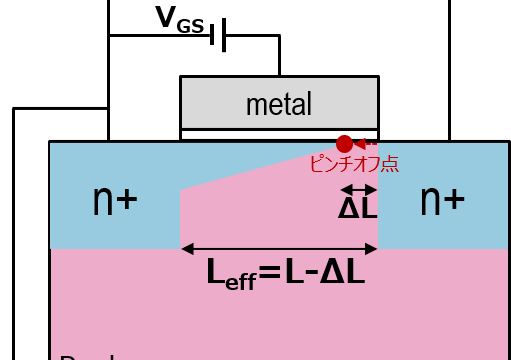

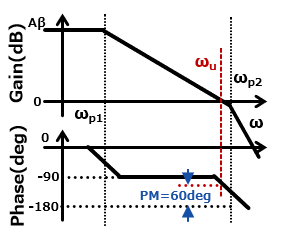

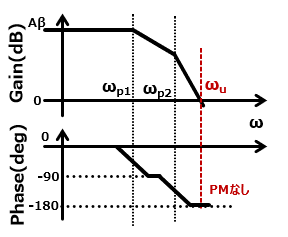

ざっくりまとめるとネガティブフィードバックを用いた2段オペアンプは安定性観点で、非常に不安定になりやすいんだったね。そして安定的な特性に近づけるためには、位相余裕(PM)を60degあたりになるまで、対処しないといけないって話だったね。

今日はその続きで、その対処として位相補償が必要になってくるよ。そして今日から触れるのはその中のポールスプリットになるよ。

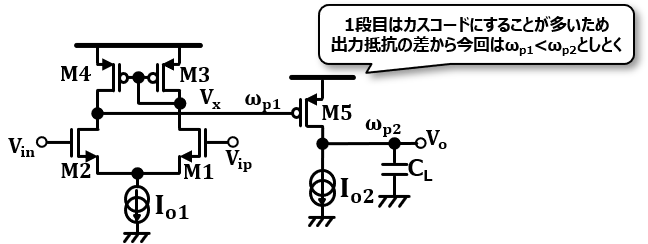

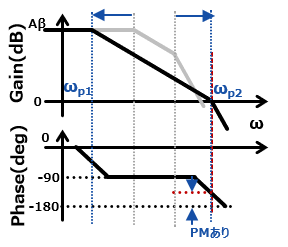

ポールスプリットとは、非常にざっくりいうと2段オペアンプにおいて近くにいたωp1とωp2を切り離すことだよ。これらが非常に近くにいたせいで、dcゲインが下がる前に位相が180degすぐに回ってしまっていたので、

これを引き離してωp2を迎える前にdcゲインを十分落とすって思想になるよ。

では具体的にポールスプリットするにはどうすればいいかを、次項で触れていこう。

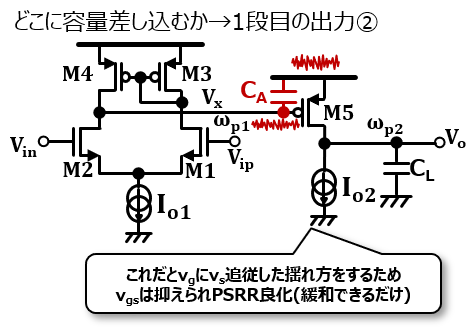

ポールスプリットするにはどうすればよいか

以前に触れた内容だけど、このポールってのは各ノードの抵抗成分と容量成分の積で決まるわけだよね。んでωp1とωp2を引き離したいってなったときに、ここでポールスプリットするには、片方のポールのRCを大きくしてもう片方のポールのRCを小さくすればいいわけだけど、RCを小さくする場合にCは次段の負荷容量とか回路仕様的に決まってしまうものなので減らすことはなかなか現実的じゃない。

一方Rを小さくする場合も、もともとdcゲインを増やしたくて出力抵抗を増やしたのに、それを減らすのであれば2段オペアンプの旨味もかなり減ってしまうかも。(実際ポールとして見えるRはポールスプリットによって小さく見せることも可能だけど、今はそう考えておこう)

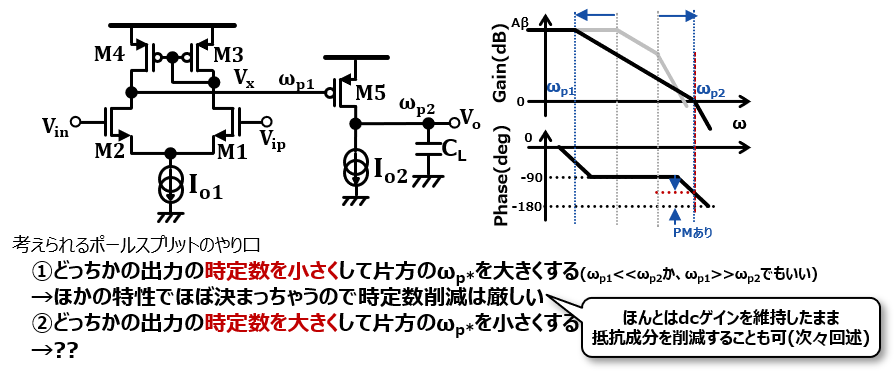

なので片方のポールのRCを大きくすることで引き離すってのがいまいま現実的なのかなと考えよう。ではRを増やせばいい?Cを増やせばいい?

ここでRを増やしても、ポールスプリットは実現できても安定性は改善しないことになるよ。その心は非常にシンプルで、Rを増やした分だけポールを低周波に持ってきたとしても、それと同じ分だけdcゲインが大きくなることになるので、結果としてユニティゲイン周波数ωuは変わらないことになるんだ。詳細は以下参照。

→acゲインとカスコード回路について

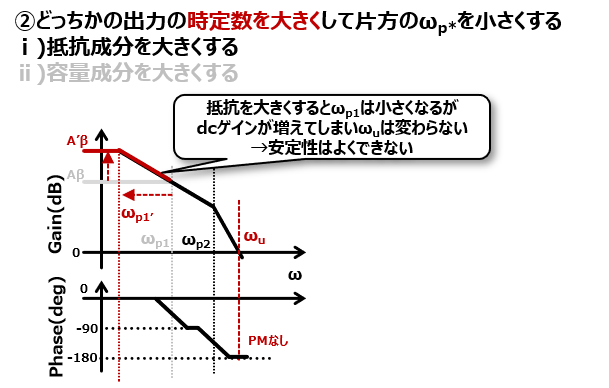

ってことで消去法的に容量を大きくして片方のポールを低周波に持ってくるしかなくなるよ。では容量を増やすにはどうすればいいかを次項から考えていこう。

ミラー容量を用いたポールスプリットが効果的か?

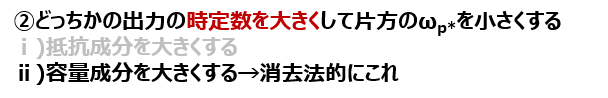

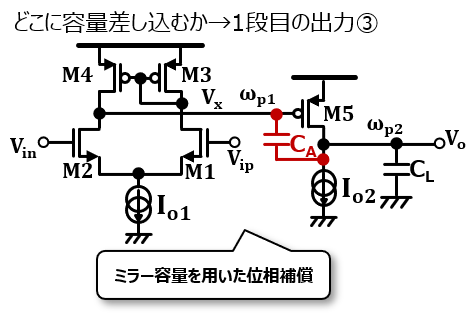

じゃあ容量を大きくしてポールを離すとなると、どこに容量を差し込んで増やすのがいいんだろうか?例えば2段目の出力段にて大きな容量を差し込むと、スルーレートが片側の極性だけかなり悪化して、立下りか立ち上がりかの特性で大きな差分が出てきてしまうね。

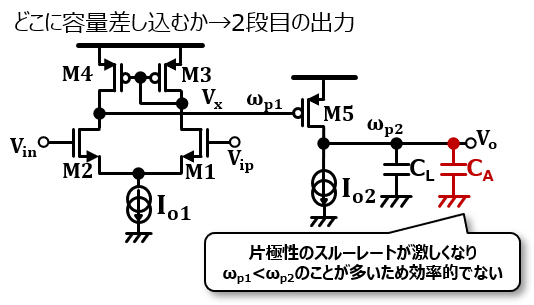

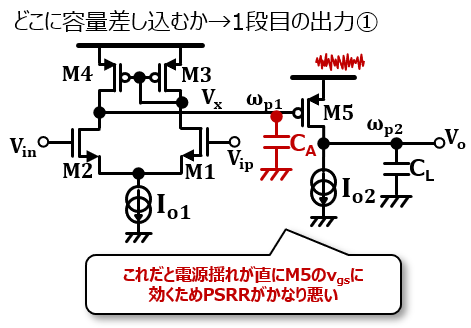

じゃあ1段目の出力(2段目の入力)に容量を差し込むとして、どう差し込むのが良いか。まずミラー容量を用いない場合だけど、電源側につなげるかgnd側につなげるかだけど、これは電源側につなげるほうが良いのかなって感じがするよ。

その心は、電源が揺れたときに入力段のnchのソースが揺れることになるからPSRRが悪化してしまうんだけど、ゲートと電源を容量を介してつなげておけば電源揺れにソースだけでなくゲートも一緒に揺れてくれることからPSRRを若干緩和できるかなって気がするので(電流源とかでサンプルホールドにしたほうが電源変動に伴うゲート揺れの感度を高められて、vgsをもっと小さくできるんだけど、入力デバイスではできない)。

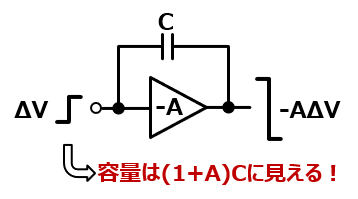

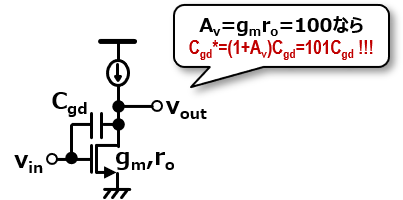

後はもう一つのオプションは、2段目でなく1段目の出力に容量を差し込む理由にもつながってくるけど、ミラー容量を用いるやり方だ。ミラー容量ってのは以前にミラー効果について触れているけど、アンプの入力と出力間に容量を挟むことで、容量を2段目のゲインだけ大きく見えてしまうって効果だね。

ミラー効果は一般的には帯域がかなり狭まってしまってよくない効果として現れることが多いんだけど、位相補償ではこのミラー容量を利用できるんだね。

→ミラー効果について

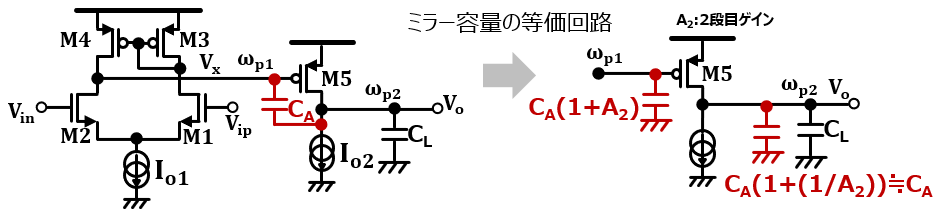

つまりはポールを引き離すのにほんとはかなり大きな容量が必要だったとしても、以下のようなミラー容量を利用した場合に正味の容量はそこまで用意しなくてよくて、面積を大きくならずに済むんだね。

ちなみにミラー容量のつなげ方にした場合、等価的には以下のような容量の付き方をするんだね。なので一応2段目の出力にも正味の容量くらいはついてしまうことには注意しよう。

じゃあ上記で二つの選択肢(②と③)があったと思うんだけど、やっぱりミラー容量を用いたポールスプリットがいいのかな?

今回の内容は以下あたりを読めば十分な理解ができると思うのでおすすめだよ。

Analog Integrated Circuit Design

次回予告

先に結論を述べると、条件によってはミラー容量を用いても全く位相補償の効果がないどころか、悪くなってしまうこともあるんだ。これは容量を介した信号経路ができてしまうからなんだね。

ゼロ点っていうんだけど、これがどんな影響を持ってしまうかを次回は小信号等価回路の観点から深ぼっていくので、その前に一度考えてみてねん。

次回→オペアンプの位相補償:ポールスプリットについて-小信号等価回路での解析とゼロ点の考慮-

余談:出力段がソースフォロワの場合

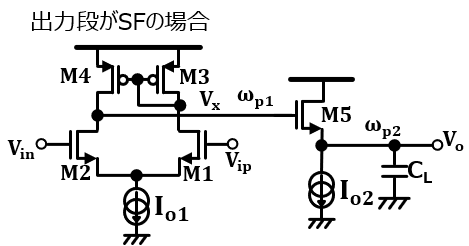

今までは2段オペアンプの2段目にはソース接地回路を用いた場合の安定性設計について触れてきたけど、以下のように出力段にソースフォロワをバッファとしておくことでDレンジを確保しつつ出力インピーダンスも減らせるってことも考えられるよね。

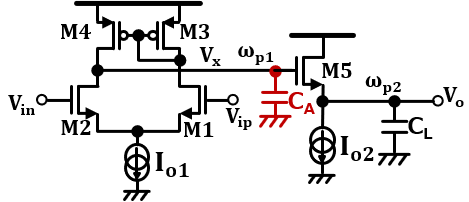

これも仮に出力段の負荷(次段の負荷容量)が大きければPMが確保できず不安定になることが多分になるよ。これの場合に同様に容量を増やしてポールスプリットを考えたときに、考えられる容量の置き場は以下が濃厚なのかなって気がするよ。

さっきとは違って電源側に置いたらvgsに対してゲートだけ追従するような形になるので、PSRRがむしろ悪くするような容量となってしまうので、gnd側につける他ないよ。

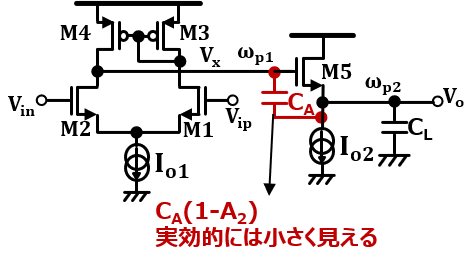

もう一つ重要なことがあって、ミラー容量を用いた場合にどうなるかな?

以前のミラー効果の記事にも少し書いてるんだけど、ミラー容量が増えて見えるのは反転増幅回路に限った話なんだね。ソースフォロワのように正のゲインがかかる場合、以下のようにA(≦1)だけ正味の容量から引かれた見え方になっちゃうんだね。

不思議なことにソースフォロワをゲイン1倍にして用いると、いくらミラー容量を挟んでも理論的には全く存在しないってことになるんだね(容量は電圧が変動しないと充放電が起きず機能しないため)。

なのでポールスプリットとしての用い方には適していないっていえるよ。容量がどうついて見えるのかってのをよく考えないといけないね。

今日はここまで、ほな。

雑談枠

ありがたいことにボーナスもらえたので、空気清浄機でも買おうかしら。空気清浄機って使う前後で違いって分かるものなんかね。気づけない健康への投資ってイメージもあるけど。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。