どうも、さわざわです。

今回はノイズについて、基礎的な部分を触れていこうと思うよ。以前にソースデジェネレーションを用いた電流源に関して、熱ノイズの観点から考察を記事にしたんだけど、ノイズの基礎を前提にした応用的な内容になっちゃったので、今回は基礎部分に絞るよ。ノイズに関してさわざわもまだまだ勉強中だけど、みんなも勉強していってねい。

この記事を読めば、熱ノイズとフリッカーノイズ、回路におけるノイズの評価について、基本的な観点を理解できます。

熱ノイズについて

ノイズを詳細に分類してくといろいろあるみたいだけど、ここでは代表的なノイズを二つだけ紹介するよ。

そのうちの一つが熱ノイズで、アナログ回路においてざっくりとは抵抗とMOSFETがノイズ源となりうるよ。これはどの周波数帯でも現れるノイズであって、ノイズ評価において絶対に考慮しないといけない要素だよ。

ノイズ電流で見ると以下のように表せて、基本的には抵抗成分が大きいほど、つまりはRは大きいほど、gmは小さいほどノイズ電流は小さくなるよ(電流として評価してたら、に注意。電圧としては抵抗が大きいほど熱ノイズは大きくなる)。あとはいずれも温度Tが高いほど大きくなるので、熱ノイズって名前の通りだね。

この要素的なノイズが小さいと、結果的には評価するノイズを小さくできるよ。これは後述するよん。

フリッカーノイズについて

次にフリッカーノイズノイズで、これはMOSFETに現れるノイズになるよ。

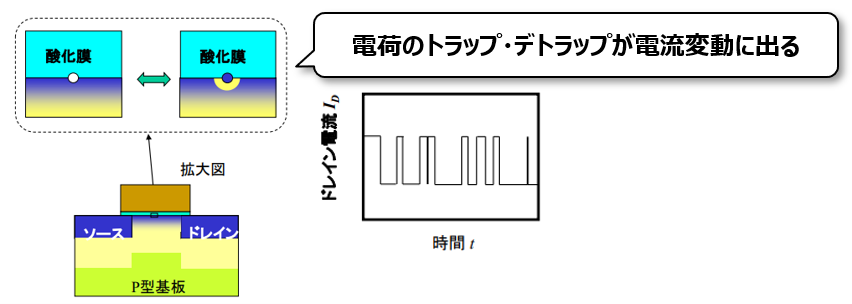

これはデバイスの話だけど、チャネルと酸化膜の界面って材料が異なることから、必ずしもきれいに材料が隔てられてるわけではなくて、電気的な移動が起こる余地があるんだ。これは以下のように電子や正孔のトラップ・デトラップを引き起こして、その際の電流変動がノイズとして現れるものになるよ。

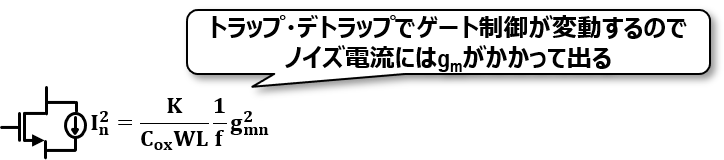

このトラップ・デトラップは低周波ほどモニタ出来て、ノイズ電流は以下のような周波数とデバイスサイズに依存した形になるよ。fは周波数で、W、L、Coxはよく知るデバイスプロパティ。

ここでのgmは、このトラップ・デトラップがゲート制御に電圧として現れて、それを出力電流として評価した際にかけて現れた値になるよ。

Kってのは製造プロセスに依存したパラメータらしくて、界面が悪化するほどトラップ・デトラップが起こりやすいわけで、プロセスにも大きく依存するノイズってことだね。

ちなみにpchは埋め込みチャネルといって、正孔が酸化膜から少し離れた位置を走ることからフリッカーノイズが抑えられ、nch入力でなくpch入力のアンプとかはそういったメリットがあるよ。(pchの埋め込みって昨今のアナログ回路で用いるデバイスでもあるんかね?)

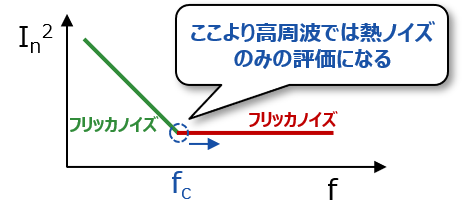

ここで周波数帯でわけてノイズを評価すると、低周波ではフリッカーノイズが支配的になる一方で、fcを超えた高周波帯になってくると、熱ノイズのみを評価する形となり、ここは回路の使用によってフリッカーノイズまで評価するか否かを判断する必要があるよ。

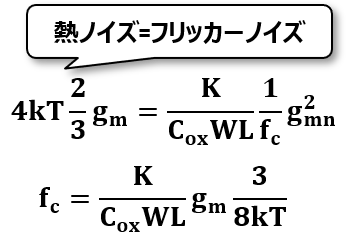

fcの時点ではMOSFETにおけるフリッカノイズと熱ノイズがおよそ同等になることから、以下のようにfcを占えることになるね。

ラザビではサブミクロンデバイスではfc=500k~1MHzらしいけど、もっと微細ではfcが高い位置にずれていくのかな?(同一面積だとCoxだけ高くなるからむしろ低くなるんだろうけど。)

入力換算でのノイズ評価の考え方

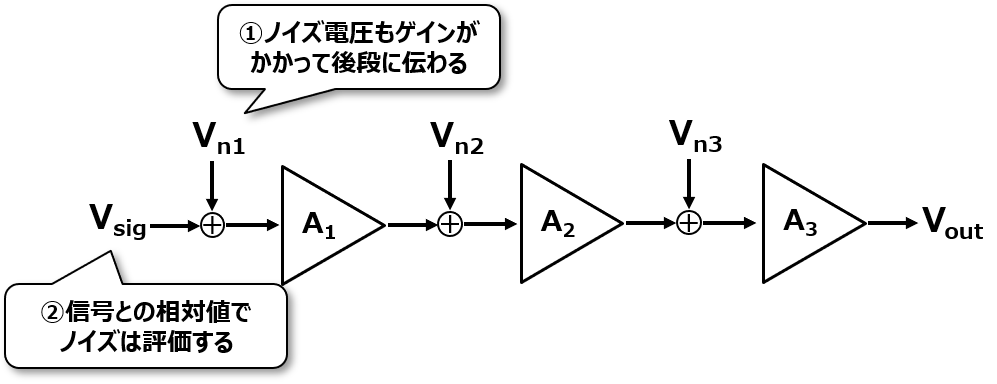

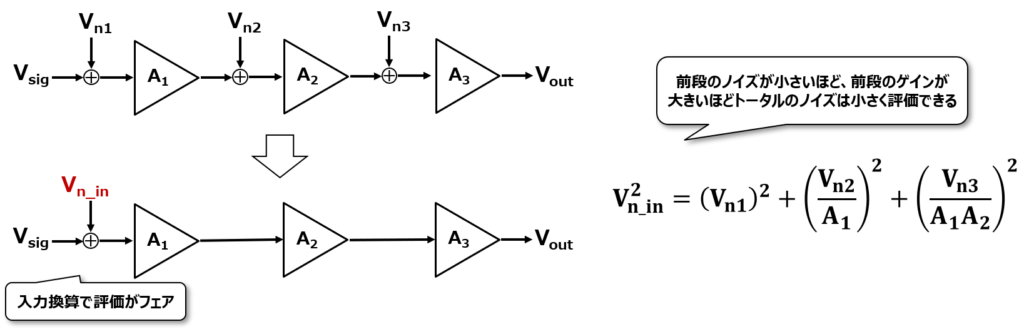

いままで要素的なノイズには触れてきたけど、これをどう評価していくかを見ていこう。例えば以下のようなブロック図があったとして、どう評価するのが正しいだろう。

まずここでは二つ重要なことがあって、一つはノイズも電圧換算したらそれにゲインがかかって後段に伝わることと、もう一つはノイズ評価はノイズの絶対値で行うのではなく本命の信号との相対値で行うってこと。

仮にノイズが大きくても、入力信号がそれよりもはるかに大きく、性能的に無視できるレベルのノイズと判断することもあり得るってことだね。

なので信号と同じレベルでノイズを評価することが必要で、その際に入力換算でのノイズ評価が一般的といえるよ。

つまり以下の部分で比較をするってことで、この際各段のノイズはゲインで割り戻された値になって、信号との正当な比較ができそうだよね。

ここで重要なこととして、各段でのゲインが大きいほど入力換算でのノイズは抑えられるってことと、入力に近いブロックで発生するノイズを抑えるほどトータルで見たノイズは小さくなるよ。

次項で実回路でノイズ評価を考えてみよう。

ノイズについては以下で勉強してももちろんいいし、

こっちでもノイズの理論的なことは良く理解できると思うよ。

Analog Integrated Circuit Design

ノイズの計算と複雑なトレードオフ

ってことでノイズを計算する際の順番としては、

①そのブロックでノイズ源となる要素を挙げる(抵抗とかMOSFETとか)→

②各要素のノイズ電流のトータルを出力ノードで見積もって出力抵抗によって出力ノイズ電圧として見る→

③ゲインで割り戻して入力換算でのノイズ電圧で見る、

になるよ。

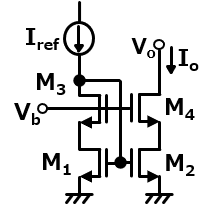

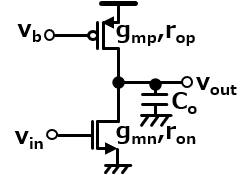

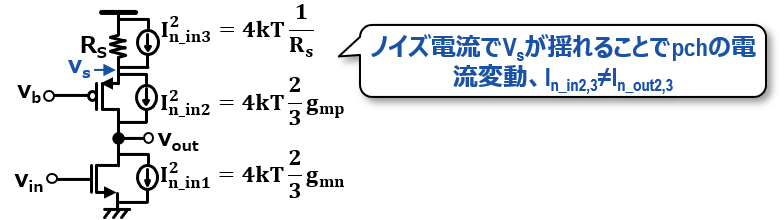

例えば↑のようなソース接地回路を例にとるけど、ノイズ源はnchとpchとRDで、それぞれノイズ電流は以下のように各MOSFETに並列する形でつくことになるよ。ここでは簡易的にフリッカーノイズは無視できるとしてるけど、フリッカーノイズを考慮する場合はnchとpchにその分のノイズ電流がさらに並列につくことになるよ。

今回の場合は、各ノイズがそのまま出力に伝わるので、出力に流れる総ノイズ電流は以下のようになるね。

ここで出力にそのまま伝わるか否かは、ノイズ電流によって出力までの途中のノードが動いて、出力に流れる電流がもとのノイズ電流だけに依るか否かになるよ。

例えば↑のソース接地回路の場合は、Inによって出力ノードが揺れてもnchやpchってvdsが変動するだけなので十分長チャネルだったらnchやpch自体の電流ってのは変動を無視できるよね。なのでIn_in1やIn_in2はそのまま出力に伝わるっていえる。(In_in1≒In_out1)

前回触れたソースデジェネレーションを用いた電流源だけど、これはノイズ電流であるIn_in2やIn_in3によってvsが変動することから、pchのvgsが変動して結果的にpch自体の電流も変動が見えるよね。これによって出力に出てくるノイズ電流ってのはIn_in2だけに依らず、ゲインがかかって出てくることになるんだ。

詳細はぜひ前回の記事を読んでみてねん。

→ソースデジェネレーションを用いた電流源とノイズについて

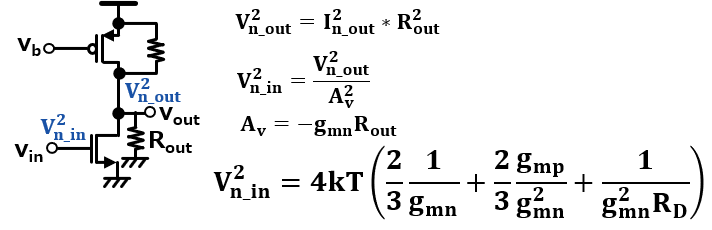

ソース接地回路に戻るけど、これに出力抵抗をかければ出力ノードのノイズ電圧となるね。んでゲインで割り戻したら入力換算のノイズ電圧が出せたよん。

ここでようやくノイズをできるだけ小さくするにはって話になるけど、gm1を大きくするのが一番効きそうで、gm2を小さくするかRDを大きくしても減らせることがわかるね。

以前も触れた重要なことだけど、入力デバイスのgm(ここでいうgm1)はゲインにかかるから大きいほうがいい一方で、負荷デバイスのgm(ここでいうgm2)は純粋に熱ノイズの観点から小さいほうがよいことになるよ。

gm1を大きくしたいとなると、Wを大きくしたり電流を増やしたりがあるけど、前者は容量を大きく動作を遅くしてしまうし後者は消費電流増加になるね(サイズアップはフリッカーノイズ抑制にもつながるけど)。

RDを大きくしようと考えるとdc的に電圧マージンを狭めてしまうし動作もまた遅くしてしまうね。

ノイズはアナログ回路において無視できない性能である一方で、これがアナログ回路のトレードオフをはるかに複雑にしているように感じるよ。電流源のノイズ低減は前回のソースデジェネレーションを用いた電流源の記事を読んでみてねん。

今日はここまで、ほな。

雑談枠

回転寿司とかであるサーモンにアボカドとオニオンとマヨネーズ乗っけたやつ、めっちゃ好きなんだけどまじで謎。なにを思ってアボカドを乗せとようと思ったのか、アボカドと他の材料の親和性ってどうやって開拓されてきたのか。料理も発明の連続をたどって進化をたどってきたんやろな、知らんけど。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。