どうも、さわざわです。

今日はチャネル長変調効果について、さっぱりと触れていきたいと思います。

チャネル長変調効果は、MOSFETの2次効果の一つでといわれていたりして、MOSデバイスの物理領域の話ではあるんだけど、アナログ回路でも出力抵抗とかにこの効果が大きく関わってきて重要なので、正しく理解しておく必要があるよ。みんなも勉強していってねい。

この記事を読めばチャネル長変調効果と出力抵抗の関係についてわかります。

出力抵抗とオン抵抗の違い

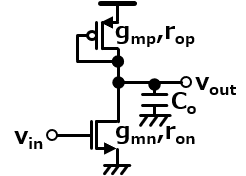

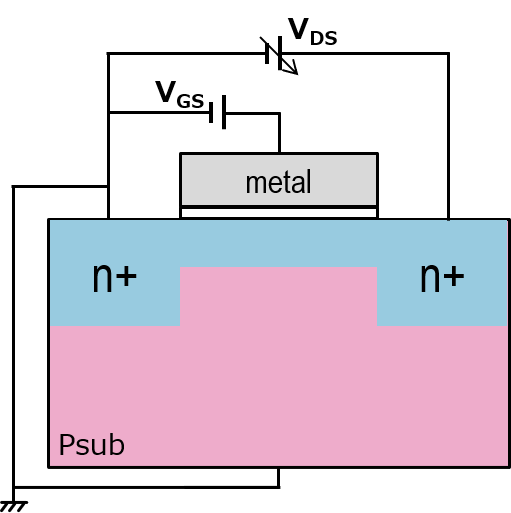

まず今回は出力抵抗について触れていくけど、アナログ回路における駆動してるMOSデバイスを用いた抵抗の考え方は大きく分けて二つあるよ。それはオン抵抗と出力抵抗だね。オン抵抗をRonとし、出力抵抗をroとした場合、この二つの違いは何かわかるかな。

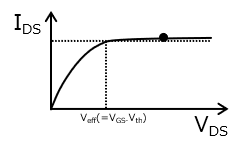

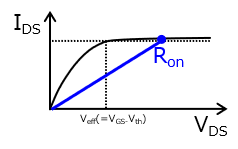

では以下はMOSの出力特性であるIds-Vdsのグラフだけど、点の位置でMOSを駆動させていた場合にroはいくつになるだろう?

これはこうなるんだね。

では同じバイアス点で、Ronはどうなるかわかるかな。これは実はこうなるんだね。

この二つの違いがわかるかな。つまりroはバイアス点におけるVdsの変化におけるIdsの変化から抵抗を引いたもの、つまり微分の結果になるよ。

一方でRonは切片を0のとこからバイアス点へ直線を引いた値で、単純なVdsをIdsで割った値になるよ。

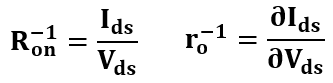

式で表すと以下のような違いだね。ここでオン抵抗はdc的な抵抗なわけで、roはac的な抵抗、つまりは小信号で考えたときの抵抗になるよ。小信号等価回路でroを扱うのはそのためで、逆にdc的な抵抗は見る必要がないんだね。

余談だけど、Vdsがかなり低い、深い線形領域で駆動させた場合、Ronとroは一致して、小信号でもRonを考える必要が出てきたりするよ。

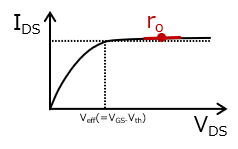

んでゲインを得るためには基本的には回路の出力抵抗を大きく見せる必要があって、そのためにはMOSを飽和領域で駆動させて、以下のようなroが非常に高い部分を用いる必要があるよ(Vdsが大きすぎればいいというわけではないけど)。ちなみにこの領域は理想的にはVdsの変化に対してIdsは一切変化しなくてroが無限のはずなんだけど、実際には傾きがあってroは有限値となってるね。

これについて触れていくよ。

チャネル長変調効果の原理

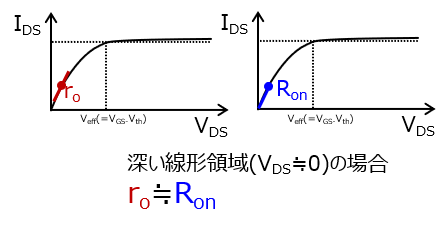

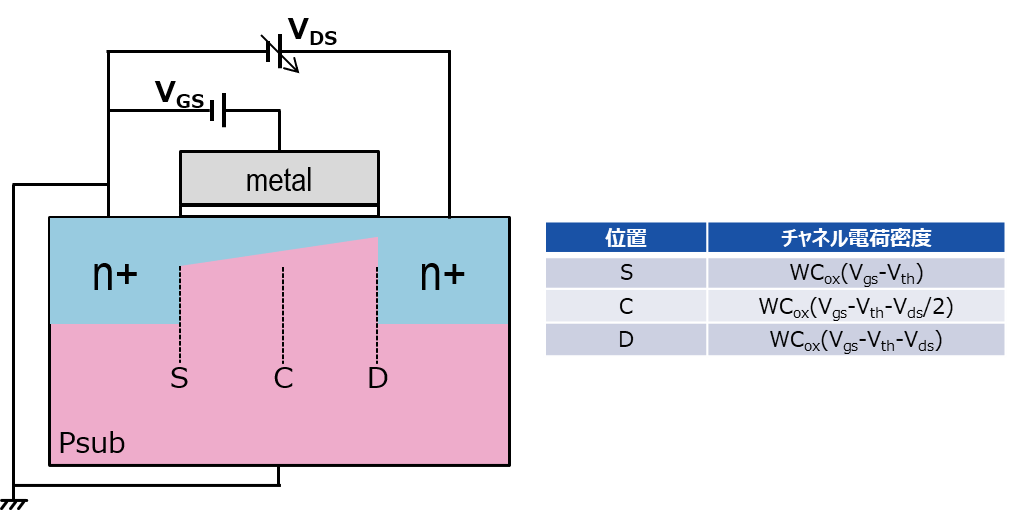

これはチャネル長変調効果といって、Vdsを増加させていったときに、チャネル長が実効的には短く見えて、電流が増加していく現象だよ。 以下はMOSのモデルだけど、Vds=0でVgsがVthより高くMOSがオンしている場合、線形領域でチャネルは平らに形成されるよ。この際、VgsがVthを超えた分だけチャネルに電荷が発生するわけで、このチャネル電荷密度はWCox(Vgs-Vth)になるよ。ここでWはチャネル幅で、Coxは酸化膜容量を指してるよ。

これにVdsを高めていくとチャネルの横方向に電圧がかかってくるわけで、酸化膜にかかる電圧がチャネル位置によって変化していくんだね。具体的にはドレイン端側にはVdsがフルでかかるので、酸化膜にかかる電圧は小さく見えて、酸化膜下に存在するチャネルの電荷密度は減っていくよ。

ソース端にはVdsがほぼかからないはずなのでチャネル電荷密度は線形のままWCox(Vgs-Vth)だけど、チャネル中央だとおよそVdsの半分がかかっているはずなので酸化膜にかかる電圧はVds/2だけ減ってチャネル電荷密度はWCox(Vgs-Vth-Vds/2)となっているよ。そしてドレイン端ではチャネル電荷密度はWCox(Vgs-Vth-Vds)となる。ちなみに一般的にこのチャネル電荷密度はVdsがあると分布があるものの、平均値のWCox(Vgs-Vth-Vds/2)で扱うよ。

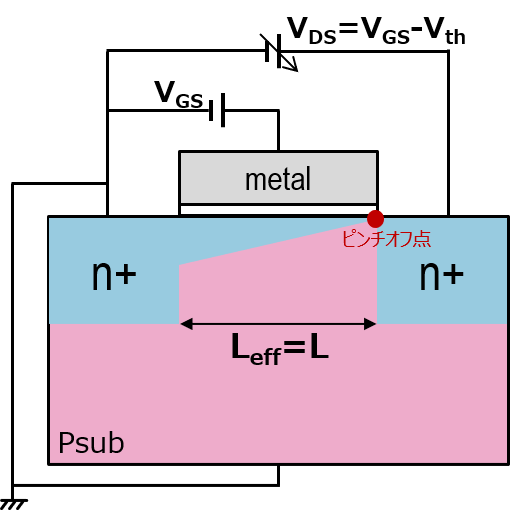

ではここでVds=Vgs-Vthになったとき、すなわち飽和領域に入ったときにどうなるかだけど、ドレイン端ではWCox(Vgs-Vth-(Vgs-Vth))=0になって電荷がなくなることになるんだね。

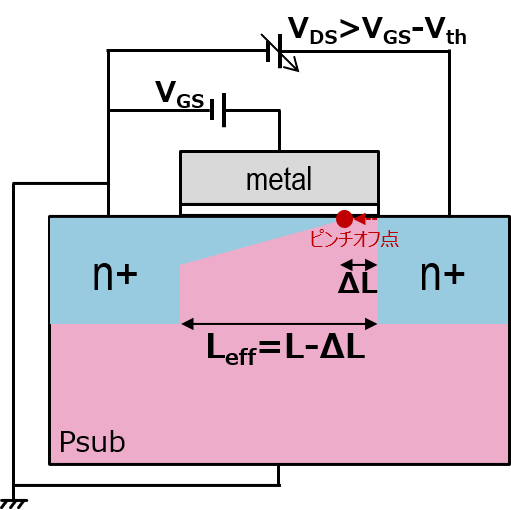

さらにVdsを上げるとドレイン端での電荷密度はマイナスに入るけどそれはチャネル電荷が発生しなくなるだけで、ただチャネル電荷密度がちょうど0になる点が少しづつソース側にずれていくことになるね。このチャネルがなくなる点をピンチオフ点なんて言ったりするんだけど、このピンチオフ点のソース側への移動は、本来Vdsに対して電流が一定であるはずの飽和領域で、実効的なチャネル長がピンチオフ点の移動分だけ小さく見えることから、Vds増加に伴い電流が大きくなる現象へと繋がるんだ。

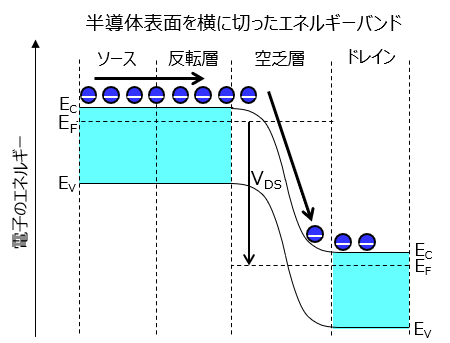

ちなみにこの時チャネル(反転層)が途中で切れちゃってるから電流は流れないんじゃないか、なんて昔さわざわは思ってたりしてたんだけど、実際はこの反転層からドレインまでは空乏層が形成されているはずで、以下のようにエネルギーバンド図で見ると、電荷はドリフト移動で空乏層を下って流れるだけなので、全く問題はないんだねん。

チャネル長変調効果と出力抵抗

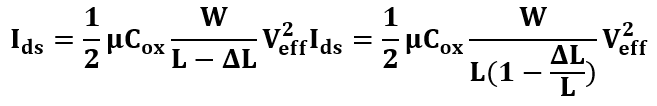

では最後にこの現象を式から抑えよう。飽和でもVds増加によってIdsが増加するということで、チャネル長変調効果を考慮すると電流式はまず以下のように表せるよ。

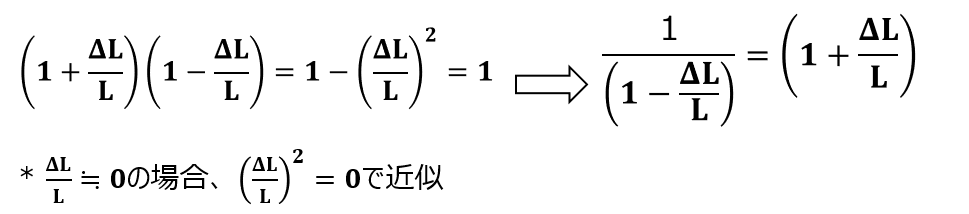

ここでΔLがチャネル長変調効果によって減少したチャネル長のことだよ。んでこれは数学的な近似だけど、ΔL/Lが非常に小さい値の場合、以下のような近似ができるよ。

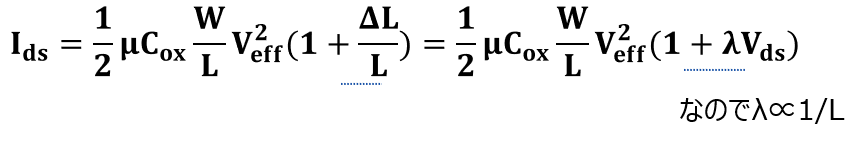

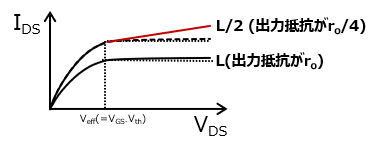

そうすると電流式は以下のように表せて、このΔL/LはVdsとの関係を一次近似してλVdsで表せることになるよ。この際λは1/Lに比例するパラメータであり、短チャネルほど以下のように傾きがIds-Vdsの傾きが急になるよ。

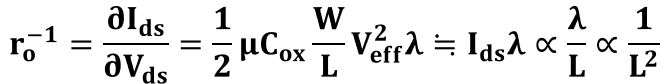

具体的には以下のような関係からL2に比例して出力抵抗roは大きくなり、短チャネルデバイスでは十分な出力抵抗が得られない、すなわちゲインが得られにくいということになるね。なのでデジアナ混在のチップを先端プロセスで用いる場合も、アナログブロックは十分チャネル長を持たせて設計することがあったりするよ。

この項の内容については以下を参照にしているので詳細はこっちもよく読んでみてねん。

チャネル長変調を含めたデバイスの基礎的な理解を深めたい場合は以下がおすすめ(初心者向けな内容を押さえつつかなり深く理解できると思います)。

半導体デバイス入門: その原理と動作のしくみ (新・電子システム工学 TKR-6)

半導体デバイスの内容をより詳細かつ網羅的に理解したい場合は以下がおすすめ。分からんときに辞書的にも役立つ。(以下はちょっと前に出た第3版。さわざわは第2版しか読んでないけど、読んでみたい。。中古なら第2版のほうがよいかも。)

固有利得の考え方

→固有利得について_dcゲイン調整と周波数応答

今日はここまで、ほな。

雑談枠

iPhone8を使ってるんだけど新しいのに買い換えたい。っていって2-3年くらい経ったような。最近のでかくて高いのでさわざわ的にはきつくって、新しく買うならSEかな。いつになるのかわからんけど。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。