どうも、さわざわです。

今回はゲインと周波数応答の関係について触れていこうと思うよ。単純なdcゲインについてはカスコード回路を用いることで高められるって話は以前にしたけど、周波数特性を考慮したacゲインだとどうなるのかって話をしていくよ。周波数帯域を気にして設計する際には基礎的かつ重要な部分だと思うし、安定性設計にも若干つながっていく内容なので、みんなも勉強していってねい。

この記事を読めば、カスコード回路を用いてゲインを上げた際の周波数特性について理解することができ、dcゲインだけでなくacゲインまでの理解を深められます。

dcゲインとacゲインについて

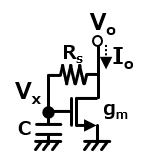

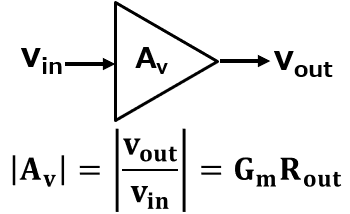

まずはゲインを増やす手法として、以前にカスコード回路をあげたね。軽く復習だけど、ゲインを上げるには回路ブロックのコンダクタンスGmか出力抵抗Routのどっちかを上げるしかないんだけど、Gmを上げるのは結構限りがあるのでRoutを上げると。

その有効的なやり口として、カスコードデバイスを用いて以下のように固有利得分だけRoutを大きくして、ゲインを上げるって話だったね。

小信号等価回路観点からちゃんと理解するには、以前の記事に詳細があるので参考にしてみてねん。

→カスコード回路について_利得に触れていく編

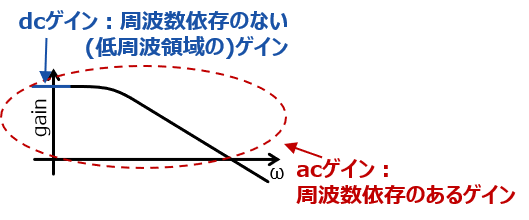

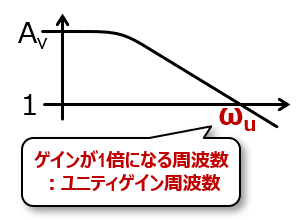

んでここのゲインってのはあくまでdcゲインの話で、ようは以下のように周波数帯域を考慮しない低周波領域での話なので、周波数特性を考慮したacゲインではどうなるのかってのを今日は考えてみよう。

カスコードでacゲインはどう変わる?

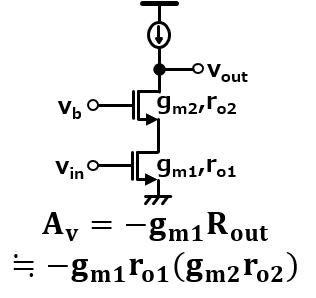

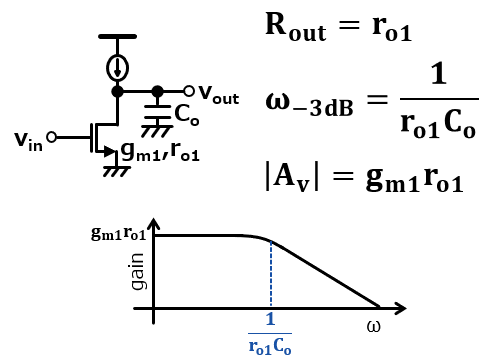

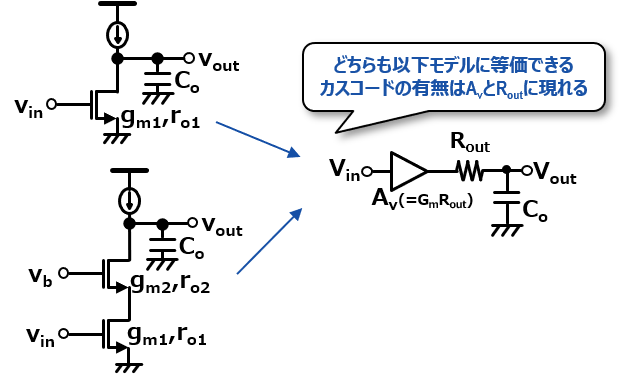

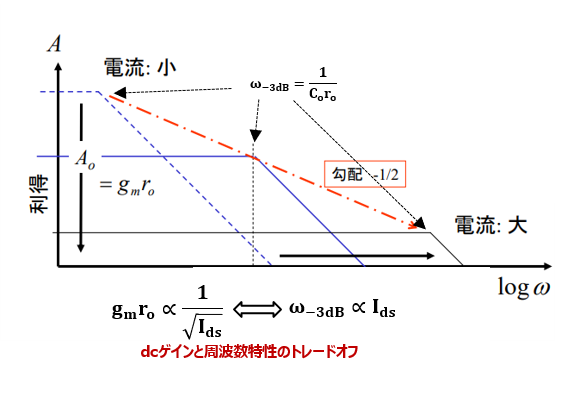

ソース接地回路の場合に負荷デバイスが定電流源だと仮定して、出力抵抗はRout=ro1で、dcゲインの絶対値はgm1ro1になるよね。んで出力ノードには負荷容量が見えているので、このノードにはローパスフィルタ(LPF)のような周波数帯域がかかり、その時定数は抵抗成分がro1、容量成分がCoであるからro1Coになるよね。

なのでその逆数にして角周波数で考えて帯域がかかりゲインが落ちていく。

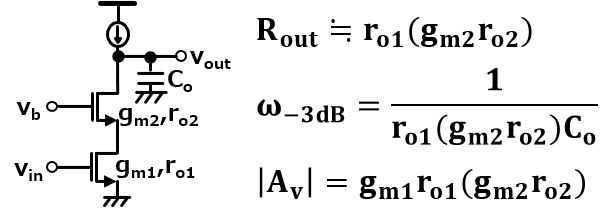

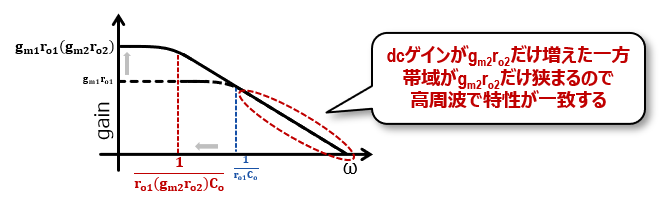

ここでカスコード回路になるとRout=ro1(gm2ro2)とカスコードの固有利得分だけ増えて(基板バイアス効果は無視する)、dcゲインはgm1ro1(gm2ro2)になるね。この際の出力ノードの負荷ってro1(gm2ro2)Coと大きな値になるため、帯域は以下のように非常に狭化されることになるね。

この際重要なのはRoutの増加によってdcゲインは増加する一方で、ゲインが落ち始める帯域はRout分だけ小さな周波数となり、高周波領域で見た際のゲイン特性はカスコード有りと無しでほぼ同等だったりもするんだ。

ユニティゲイン周波数と出力抵抗について

これはユニティゲイン周波数といってゲインが1倍になる周波数を考えたときに答えがわかるよ。

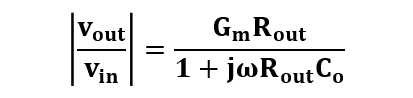

ソース接地のモデルは以下のようなローパスフィルタにdcゲインをかけたようにかけるね。

この際カスコードを追加するとAvとRoutが変化するだけで、CoやGmには変化を及ぼさないんだね。

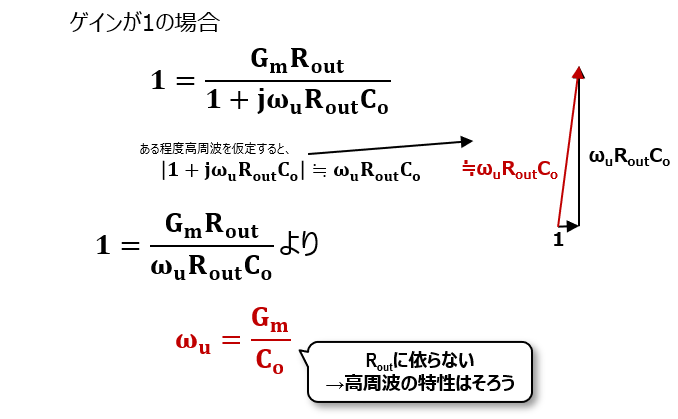

んで上記等価モデルの伝達関数が以下のようにかけて、この際のゲインが1になる周波数を計算すると、以下のように高周波である近似からユニティゲイン周波数が計算できるよ。

これからわかるように、ここに出力抵抗に関わるパラメータは依存しないことになるんだね。そのため高周波になるにつれて到達する特性は等しいことが言えるので、低周波でdcゲインと帯域の帳尻があって、高周波での特性はカスコードなど出力抵抗を利用したものでは変化がないことになるんだ。

ここでユニティゲイン周波数を変化するのにはGmかCoをいじる他ないってことだけど、これは位相補償の話題にも別途つながってくるよ。またの機会に記事にしていくね。

ここら辺の話は安定化設計でも応用されているので読んでみてねん。

→オペアンプの位相補償:ポールスプリットについて-基礎概念を理解しよう編-

カスコードで周波数特性が改善するケース

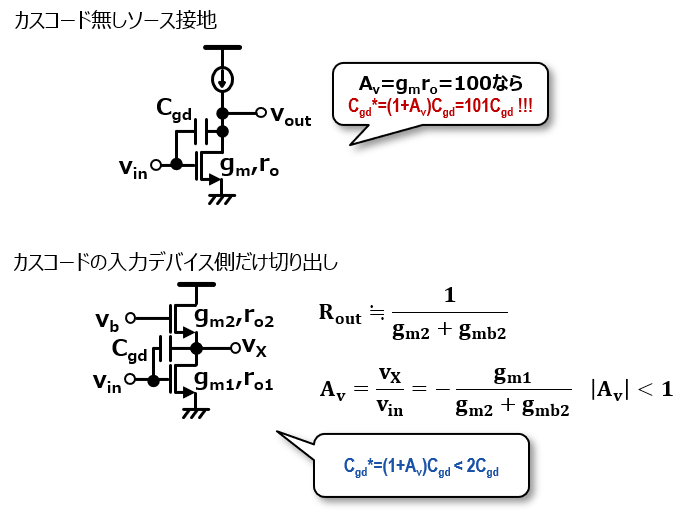

ところがカスコードが帯域改善することにも役立つケースがあるよ。というのもミラー効果を抑制できるからなんだね。

詳しくは以前の記事に譲るけど、カスコードデバイスによって中間ノードを挟むことで、本来ゲインが丸々容量にかかって見せる点を、大体2倍くらいの大きさまで抑えることができるんだね。なので帯域はRout増加分だけ狭まるといっても、Coのほうをカスコードによって減らせることができてるから、実際には上記よりもかなりいい周波数特性を持つことになってるよ。

カスコードってのはほんとにすごい発明なのがわかるよね。

→ミラー効果について

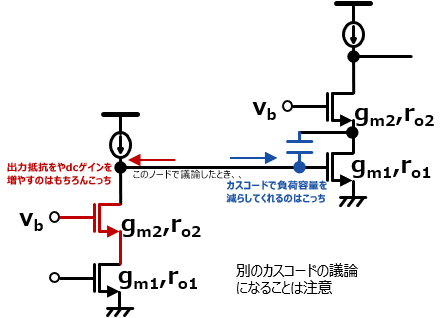

ちなみに注意として上記のように出力抵抗を増やしつつ負荷容量を減らせて、ゲインと帯域の両方を改善で来てるってのは以下のようにシリアルにカスコードを並べた際になることは注意が必要だよね。というのも以下のポールを考えた際に抵抗成分が効くのは1段目の出力抵抗が支配的になりそうで、これは先述したようにゲインを上げる一方でその分帯域は下がってるわけだね。

んで容量成分だけど、ここだと2段目のゲート容量が支配的なだけでなく、ミラー効果によって非常に大きく膨れたCgdが見えてしまっていて、カスコードでは後者の部分を低減していることになるわけだよね。

このように出力ノードに効いてくる抵抗成分と容量成分で支配的に効いてくるのが異なるブロックを跨いだ議論をなるので、設計に応じて使い分けが必要かな。

帯域を広げるには?

カスコードだとdcゲインを挙げられる一方で、出力抵抗が増えることから帯域は狭まってしまうことを説明してきたね(入力ノードに見える容量のミラー効果は抑えられるけど)。じゃあ帯域を広げるにはどうしたらいいかって話だけど、ここら辺は以前に述べてることが多いかも。

例えば駆動電流を上げることで固有利得のdcゲインは下がる一方で帯域は広げることができるんだったね。いつだってdcゲインというのは電流と面積のペナルティを負えば稼ぐことができるわけで、広帯域のアンプを多段に接続すれば高周波応答かつゲインの大きなアンプは実現できることになるね。

固有利得と周波応答については以下の記事を参考にしてみてね。

→固有利得について_dcゲイン調整と周波数応答

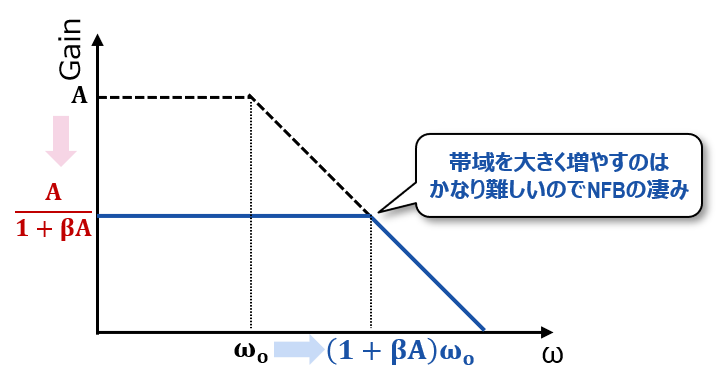

後はネガティブフィードバックを用いて広帯域化をする。これも上記と同じで、アンプ単体のdcゲインは下がるけど、帯域は広げられることができるね。

これも以前の記事を参考にしてみてね。

→ネガティブフィードバックについて

ただこうしてみるとdcゲインと周波数帯域ってのはトレードオフになることが多いっていえるね。(まあ本質的には言ってることはあまり変わらないような。)

後はインダクタとか容量を用いて、あえて二次の伝達関数を作ってパラメータを最適化することで帯域を広く見せるピーキング技術とかがあるよ。

正直これって回路的にはすごい面白いからさわざわは好きなんだけど、どれくらい用いられてるのか気になってる(さわざわは使ってるチップは一度だけ見たことある)。これはトレードオフとして安定性をかなりケアすることが必要になるよ。

詳細は別途記事にしてみたよ!

→ピーキング技術(後日公開)

ちなみにノイズ観点で入力換算で考えたらゲインは大きいほうがいいんだろうけど、帯域が広いと高周波成分までノイズがカットされないことになるので、その考慮は必要なことに注意しよう。

今日はここまで、ほな。

雑談枠

GWに帰省したのだが、我が故郷、ハトのカーストが高すぎるような。道の真ん中をハトが歩いて、我ら人間は道を譲ってる光景、昔はなんの疑問も持っていなかったが別の街に住んでから変わってるのかなと思ったり。まあ平和の象徴っていうし、確かに平和感あって構わんのだけれどね。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。