どうも、さわざわです。

今回はカスコードカレントミラーの出力抵抗について、実設計観点で深掘りをしながら触れていこうと思うよ。カスコードカレントミラーの理論ってのは以前に記事にしたけど、実際にシミュレーションしてみると理論とは異なる部分があるよ。ではどう設計したらよいか、みんなも勉強していってねい。

この記事を読めば、カスコードカレントミラーの出力抵抗における理論と実設計のギャップについて理解でき、カスコードカレントミラーの理解をさらに深められます。さらに設計観点でのヒントが得られます。

出力抵抗について

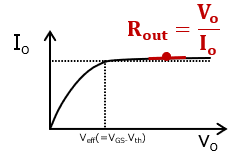

まずは復習だけど、出力抵抗ってのは以下のようにVoに対するIoの傾きから出せたね。なので電圧変動に対して電流が変動しにくいほど出力抵抗は大きいってことになるね。

なのでこの飽和後の傾きを寝かせて出力抵抗を大きくしたいわけだけど、チャネル長を大きくするほかにカスコード構造を用いるやり方があったね。これに対してペナルティは、全員を飽和で動作させることが前提なので、動作マージンを喰ってしまうことだったね。

以下の記事に詳細に説明しているので、読んでみてね!

→カスコードカレントミラーについて

実際の出力抵抗とカスコードカレントミラー

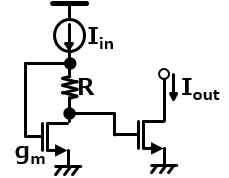

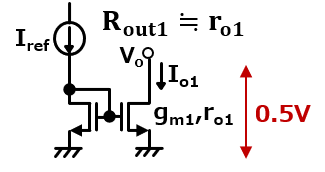

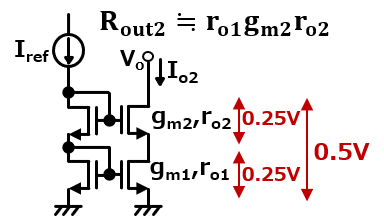

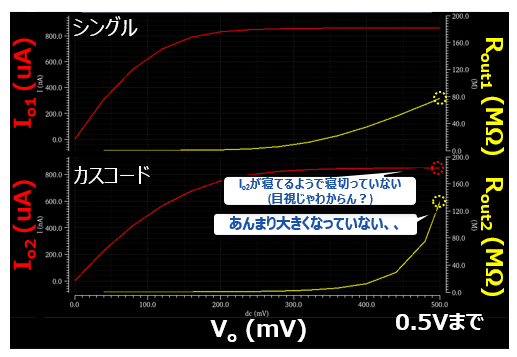

では以下の例を考えてみよう。シンプルなカレントミラーとカスコードカレントミラーだけど、どちらも0.5Vかけて駆動したとしよう。このとき全てのnchのプロパティは同じとして、Veff≒0.2Vとかとして全員飽和で動作できていることになるね。

ここで二つの出力抵抗の差を予想してみよっか。固有利得gmro=30とかにしておこう。

ここで出力抵抗の理論式は、基板バイアス効果は無視した場合に↑のようになっていたよね。つまりは同じプロパティ素子で見た際は、出力抵抗ってgm2ro2分だけ大きくなって出てくることになるよね。

なのでシンプルなカレントミラーの出力抵抗をRout1=ro1と文字で置いた際に、カスコードカレントミラーの出力抵抗はRout2=ro1*gm2ro2=30Rout1ってなるはず。そう望んで設計したい、、!

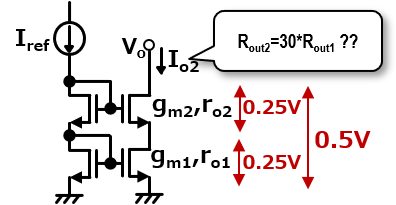

でも実際はここまでカスコードカレントミラーの出力抵抗が大きくなってくれないことがあるんだ。その心は、roってパラメータがVdsに非常に敏感だからなんだ。

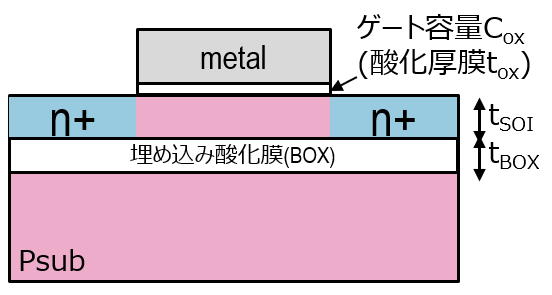

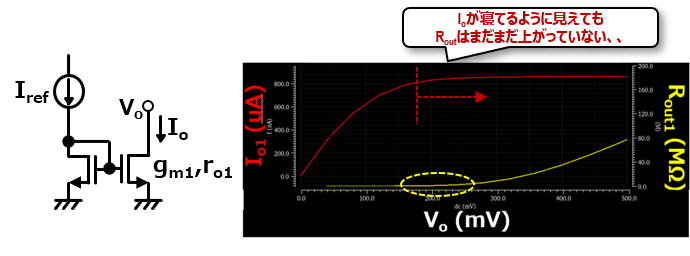

以下のように1つのMOSを考えるけど、VdsがVeffを超えれば飽和領域に入れることができる。ここからはroがほぼ一定になると思いきや、実際にはVeffを超えた後も徐々に傾きが寝るような形になるんだ。特にVeffを超えた直後はまだroが大きくなっていなかったりするよ。

だから以下の図のように、VdsがVeffを超えてからroは急速に上がり始めて、同じプロパティのMOSでは0.5VのVdsがかかるnchと0.25VのVdsがかかるnchで出力抵抗は大きく異なるんだ。

ってことでシングルの電流源の出力抵抗をそのままro1、カスコードの電流源の出力抵抗をro1′とかにしとくと、今回の条件ではVdsの違いからro1>>ro1’となり、ro1’にgm2ro2=30をかけて大きくしても、思ってたより大きくならない現象が起こるんだ。

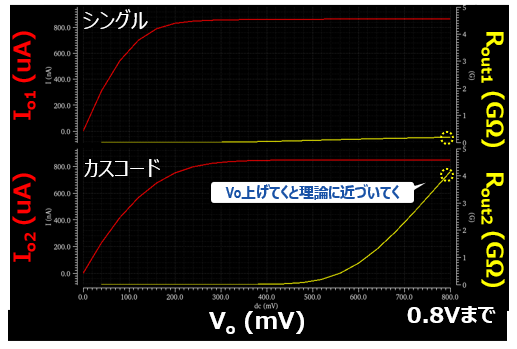

もちろん以下のように動作電圧をさらに大きくしていけば、ro1’がro1に近づいていき、やがてはシンプルカレントミラーの固有利得倍の出力抵抗を実現できるよ。

重要なのは同じ電圧動作マージンで設計する際に、必ずしもカスコードカレントミラーがのほうが出力抵抗が大きくなるとは限らず、電圧マージンによってはより多くのVdsを単体のnchにかけられるシンプルなカレントミラーのほうが良い場合だってあるんだ。

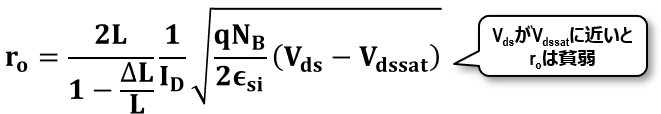

ちなみに上記はチャネル長変調効果を噛み砕いていった現象であることは分かると思うけど、厳密な出力抵抗の式は以下のようにかけるようだよ。これからもVdsにかなり依存が強く、ピンチオフ点が始まる時点のVdsであるVdsatに近いバイアス点だと、出力抵抗が非常に貧弱になりうることがわかるかな?

これがIdsだったりチャネル長変調のΔLだったりが含んでいるから、決して単純には出力抵抗を計算はできないわけだけど、ここでは十分なVdsを持たせないとroが増えてくれないケースがあることを覚えておこう。

チャネル長変調効果は以下を読んでみてねん。

→チャネル長変調効果と出力抵抗について

それでもカスコードの利点は大きい

補足だけど、それでもカスコードカレントミラーの利点は大きいよ。なぜなら根本の電流源をカスコードによってシールドできるからだね。

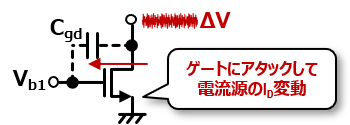

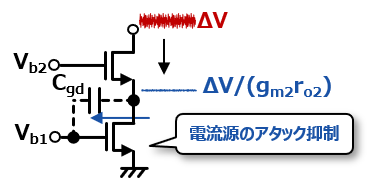

復習だけどゲート接地を挟むことで、出力で電圧がΔVだけ揺れてもカスコードのソースはΔV/gm2ro2の揺れに抑えることができるんだね。

でも結局電流源のro1’が小さいってことは、ΔIdsはドレインの電圧変動に対してro1’で割って算出するから電流変動はそんなに抑えられないって思うかもだけど、以下のように寄生容量を介したゲートへのアタックを防げるんだ。ゲートが揺れてしまうと直に電流誤差となるので、これは大きな利点といえるよ。

カスコードカレントミラーの設計の仕方の一例

じゃあ最後にカスコードカレントミラーの特性を活かすには、どう設計すればいいのかについて考えよう。前提としてアナログ設計には色んなトレードオフがあるわけだけど、今回は出力抵抗に注目しての話になるよ。

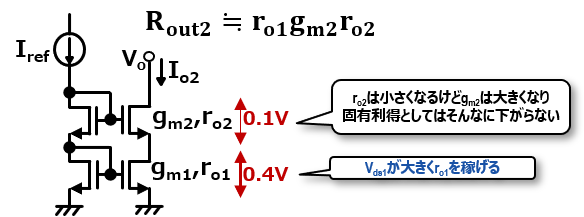

一つの答えとしては、カスコードデバイスよりも電流源デバイスを比較的長チャネルに設計することだよ。

例えば0.5Vの電圧を電流源に当てられるとして、先ほどのように同じプロパティの素子を用いて0.25Vずつ駆動するのではなく、二つのアスペクト比を調整してカスコードデバイスに0.1V、電流源に0.4Vかけるといったことだね(どちらも飽和が前提)。

カスコードデバイスは電圧がかからないことからro2が下がることは、先ほどの話からも理解できると思うけど、カスコードデバイスが出力抵抗に供給するのはあくまで固有利得gmroなわけで、チャネル長Lを相対的に小さくしてroが下がってもgmはルートに比例して上昇するので、固有利得はそんなに減らずに困らない(一応チャネル幅Wを大きくして稼ぐこともできる)。

一方で電流源は出力抵抗にroが直に効いてくるわけなので、チャネル長を大きくしてVdsを強くかければ大きなro1を達成できるよ!

この結果として、最終的なRoutはカスコードデバイスと電流源のプロパティを最適化することで、同じ電圧マージンでも高くすることは可能だよ。

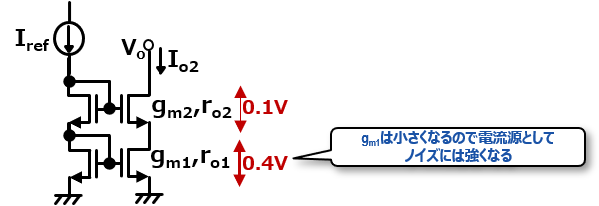

ちなみに上記の利点は他にもあって、電流源のLを大きくすることでgm1は小さくできてるよね。以前にも触れたけど、電流源のgmは小さいほうが他のノイズを伝達しにくく、電流源自体もノイズ源となりにくいよ。これは以下の記事を読んでみてね。

→ソースデジェネレーションを用いた電流源とノイズについて

今日はここまで、ほな。

雑談枠

花粉でくしゃみしすぎて腹筋つりまくり。この闘いが終わったら腹筋バキバキになってるまである。また強くなっちまうってわけ。嗚呼、負けてみてぇ~。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。