どうも、さわざわです。

今回は電源電圧不感型バイアス回路について触れていこうと思うよ。以前にカレントミラーなど、バイアス生成回路について触れていったけど、レファレンス電流の精度を悪くする要因っていくつかあって、そのソリューションとして色んな設計的な工夫が成されているよ。今回は電源電圧の変動にかかわる話。みんなも勉強していってねい。

この記事を読めば電源電圧不感型のバイアス回路について、基礎原理や応用について理解することができます。

Contents

電源電圧変動のバイアス電流への影響

以前にカレントミラーを用いてレファレンス電流からコピーして正確に各回路へと所望の電流を供給するって話をしたけど、リファレンス電流の生成として誤差の要因はいくつかあるんだね。その一つが電源電圧の変動だよ。

その前にカレントミラーの記事を先に読んどくことを勧めとくよ!

→カレントミラーについて

カスコードカレントミラーについて

低電圧カスコードカレントミラーについて

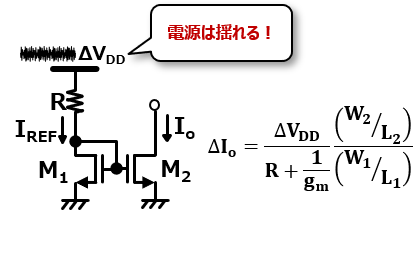

今までアナログ回路の特性を解析するうえで、電源電圧はdc電圧でのみ扱って、基本的に固定値から変化しないものとして扱っていたよ。しかしながら実際は電源電圧は揺れて、ノイズとして出力に現れることがあって、これを考慮する必要があるよ。

電源電圧変動が回路出力に与える影響をPSRRって指標で評価したりするけど、これはまたそのうち記事にしよう。

ここでは以下のようにレファレンスからIoを作ろうとすると、Irefを生成するのに電源電圧を用いているため、もし電源電圧が変動していたらその分がIoに現れることになるよ。

電源電圧不感型バイアス回路

これを防ぐためには、Ioが電源電圧の依存を持たなくなったIrefをコピーして電流を作ればいいように、Irefも電源電圧依存を持たない電流からコピーしてくればいいんだ。

つまりは”電源電圧不感のIrefからコピーしたIoをコピーしてIrefを作れば”いいんだ!

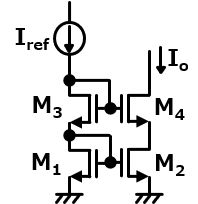

ごめん、詳しく説明するよ。以下の回路がその例となってるよ。

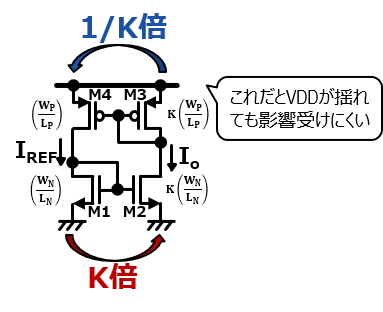

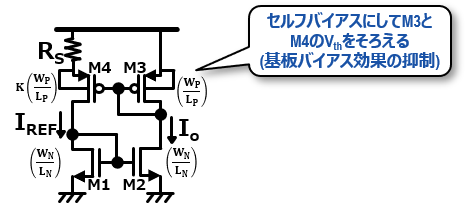

このように同じ電源電圧から、お互いを参照しあって電流を生成することをセルフバイアスっていうよ(バックゲートを自身のソースにつなげることもセルフバイアスっていうけど、意味が違う)。こうすることで、電源電圧の依存性をキャンセルできるんだ。

お互いを参照しあうわけだから、電流ミラーはK倍と1/K倍を繰り返して、Io=K*Irefの関係で安定点を取るよ。

ここでいう安定点ってのは二つあって、一つは電流がどちらかにも流れなければコピー先も電流を流さないので、お互いに電流を流さず安定になるってことと、もう一つは片方に電流が流れ始めれば、お互いを参照し始めてどちらも定常的に電流が流れて安定になるか。

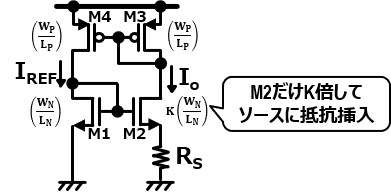

そしてこのままではIrefは所望の値に調節できず、Ioutも決められない。なので以下のように、M2のソースに抵抗を挟んでM3でなくM2だけK倍の大きさにすることで、電流の安定性を利用しつつVgsのアンバランスをわざと作って、Ioの値を決めるよ。

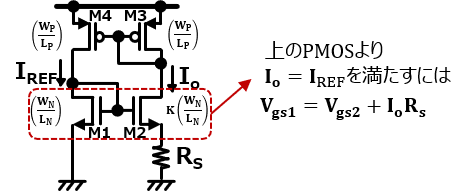

RsにIoが流れることによってM2のソースは電位を持ってM2の電流を下げようとするけど、上のPMOSカレントミラーは同サイズであることからIref=Ioで安定点を取ろうと働くよ。

なので下のNMOSもIref=Ioとなるように電流を流そうとするわけだけど、サイズがアンバランスであることからその分をM1とM2のVgsを揃えるようにM2のソース電位を調整しようとIoとIrefがともに変動するよ。

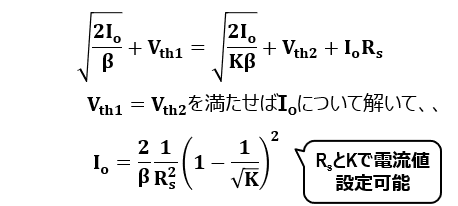

つまり以下のような関係からIoを算出することができるよ!これによって、電源電圧がずれても変動するパラメータが含まれないことから、電源電圧不感のバイアス電流を作ることができたね。

実用的な電源電圧不感型バイアス回路

この回路の懸念点を二つあって、一つはVth1=Vth2とする必要があること。同じプロパティのデバイスであればいいだけではなく、M1のソースがgndにつながっているのに対してM2のソースは電位を持ったアンバランス構造になっているため、M2が基板バイアス効果を受けて、Vth2がVth1からずれてしまう。

これには基板バイアス効果を受けないようにM2のボディをソースに接続してVbsの変動を見せないセルフバイアス構造にしないといけない(この記事ではセルフバイアスがダブルミーニングでわかりづらいね、、)。

NMOSでもディープnウェルにしたらできるけど、以下のようにPMOSのソースに抵抗を挟む形にしておけばセルフバイアスが容易にできるね。

ちなみにこの基板バイアス効果の話はソースフォロワの記事で詳しく述べてるよ。

→ソースフォロワについて

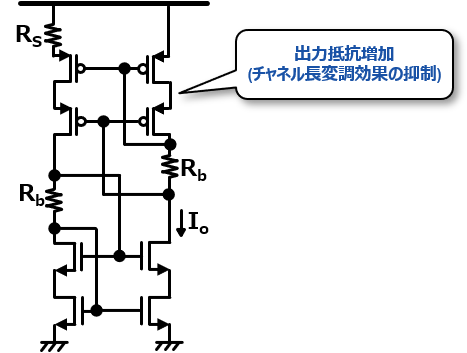

もう一つの懸念として一般的なカレントミラーで述べたように、チャネル長変調効果によってそもそものミラー精度が落ちるってことだね。これを防ぐためにはカスコード構造にして出力抵抗を大きくすればいいってのが以前までの記事の内容で、以下のように改善することができるよ。

ここで低電圧カスコードカレントミラーを実現するために、PMOSとNMOSの間に適切な大きさの抵抗が挟んであるよ。この抵抗の決め方は低電圧カスコードカレントミラーの記事を読んでねー。

→低電圧カスコードカレントミラーについて

ちなみにここでは電流調整をしているRsやKのパラメータを含んでるMOSじゃないほうでダイオード接続する必要があるよ。これはこの後記載するスタートアップ回路において、RsやKといった電流調整のパラメータを効かせないためだよ。

スタートアップ回路

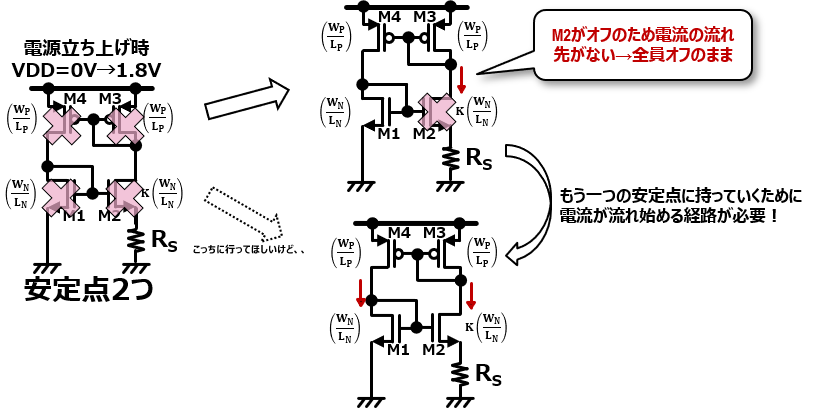

この回路は二つの安定点を持つって話をしたけど、チップの電源電圧を起動して、例えばVDDが0V→1.8Vとかに上がったときに電流を流す安定点にもっていかないといけないよ。

下のままだとVDDが与えられてもダイオード接続であるM3が電流をまず流そうとしてもM2が駆動していないことから電流経路がなく、M1~M4がオフのまま電流を流さない安定点を持ってしまうよ。右下のような電流を流しあう安定点にするにはスタートアップ回路を入れる必要があるよ。

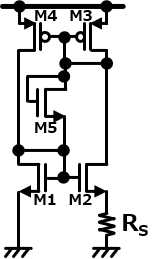

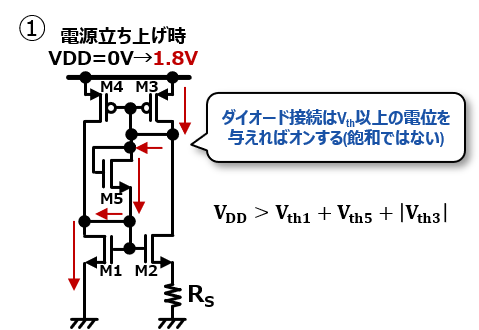

以下がスタートアップ回路を入れた電源電圧不感型のバイアス回路になっているよ。M3のPMOSダイオードとM1のNMOSダイオードの間にM5のNMOSダイオードを挟んだ形になってるよ。

まず飽和状態になる前に各MOSをオンして電流を流す経路を作る必要があって、VDDが与えられるとダイオード接続であるM3がVth3以上のバイアスが与えられることでオンするね。さらにM5もダイオード接続であるわけだからVth5以上のバイアスがあればオンして、最後はダイオード接続M1がVth1以上のバイアスでオンするよ。つまりまず以下のような条件を満たす必要があるよ。

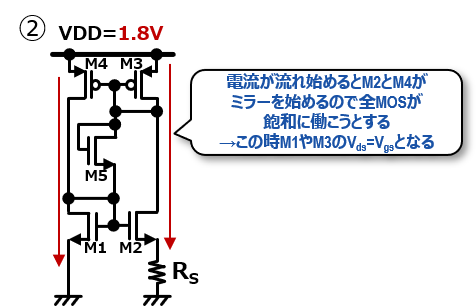

やがてM1にはVgs1までバイアスがあがって飽和で動作し、それにつられてカレントミラーが動作しあってM1-M4は飽和で駆動されるようになるよ。

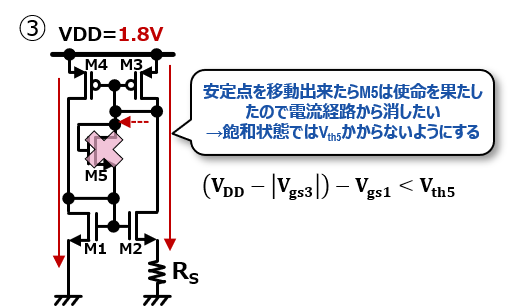

ここで起動したら、M3の電流はM5の経路も持ってしまわないようにしないといけなく、M5のゲート・ドレインとソースの間にVth5のバイアスがかからないように設定し、スタートアップ後はM1とM3が飽和になるにつれてM5はオフにするようにしよう。

つまり条件は以下も満たす必要があるよ。

より詳細を知りたい場合は以下を読んでみてねん。

電源電圧不感型バイアス回路を用いた温度不感gmの生成

最後にこの電源電圧不感型のバイアス回路を応用した例として、プロセスパラメータに依存しないgmの生成を考えるよ。

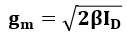

gmって以下のように表せたね。

んでここのβの中身ってのが温度依存やプロセス依存が激しくって、まずプロセス的な誤差にはCoxやW/Lのばらつきに影響するよね。

あと大変なのは移動度で、移動度は依存性を強く受けるんだ。例えばnchって高温で動作させると、Vthが下がるんだけど、それでオン電流があがるかというと、むしろ下がるケースがあるんだ。それはVth低下以上に移動度が低下して電流を小さくしてしまうからなんだ。

んで電圧不感型のバイアス回路のバイアス電流を用いるとこのIdにさっきの値が代入されるわけだから、以下のようになるよね。ここでβはきれいに削除できることがわかるかな。Rsは線形抵抗なので、実際にはこの子も温度やプロセス依存を持つんだけど、その依存性はもともとのgmより弱められるよ。

スイッチとして使われるMOSは線形動作しているため、そのオン抵抗はgmの逆数になることから、このバイアス電流を用いることでオン抵抗の温度依存性を抑えられて、精度の良いスイッチトキャパシタ回路の実現に活用できるよ。

今日はここまで、ほな。

雑談枠

企業型DCって条件によっては結構お得だなと思う、今日この頃。会社に感謝したるか。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–