どうも、さわざわです。

今回はスルーレートについて触れていこうと思うよ。オペアンプの動作保証を考えるうえで、スルーレートはセトリング特性を制限してしまって、考慮すべき重要な特性だと思うよ。みんなも勉強していってねい。セトリングについては以前に触れているので、良ければ先に読んでみてね!

→時定数とセトリングについて

この記事を読めばスルーレートについての基本的な考え方がわかり、どのような条件でスルーレートを考慮すべきかを理解できます。

Contents

オペアンプの理想的なセトリング特性

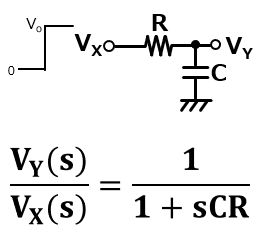

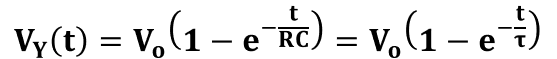

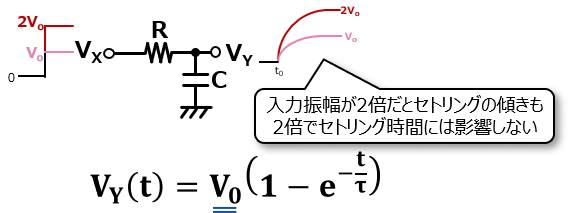

まず軽く復習なんだけど、RCのローパスフィルタの伝達特性を考えよう。

これはセトリング特性の記事にて詳しく解説しているけど、以下のように時定数に応じたセトリング特性を持つんだったね。

つまりは2倍の電圧を入力にいれるんだとしたら2倍の傾きでセトリングするわけで、このVoはセトリングに関係を持たず、セトリング時間は以下のように表せるんだったね。

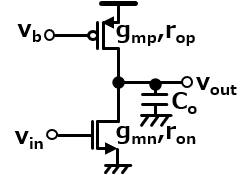

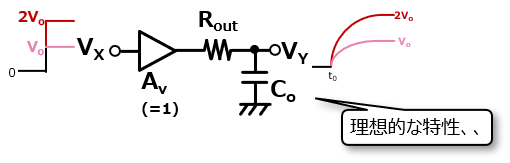

これがオペアンプの場合はどうなるかだけど、簡単化のために以下のようなユニティゲインバッファで考えよう。

以前の復習だけど、こういったアンプであっても基本的な考え方はローパスフィルタと変わらなくて、以下のような出力抵抗Routと負荷容量(出力容量)Coでローパスフィルタを組んで、そこにdcゲインをAvかけたような値になるんだったね。これについては以前の記事で述べているので、読んでみてほしい。

→オペアンプの基礎特性ついて_伝達関数と周波数応答

んでユニティゲインバッファだと、クローズドループゲインが1になるので、Av=1とするとローパスフィルタと等価と考えられるね。

ってことでローパスフィルタと同様に、入力電圧振幅Voを2倍にすると2倍の傾きでセトリングしていって、セトリング時間は入力応答ではなくほぼ時定数に支配されるってことになるね。でもこれは理想的な応答なんだ。

実際にはもっとセトリングが遅くなるケースが多くて、それについて次項で見てみよう。

実際のセトリング特性

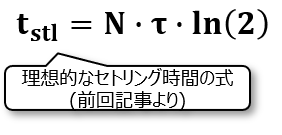

まず上記であげたオペアンプの場合は差動になっていて、電圧が変動するとその分だけ出力容量に充放電される電流量が変動して、セトリングに起因してくるんだね。

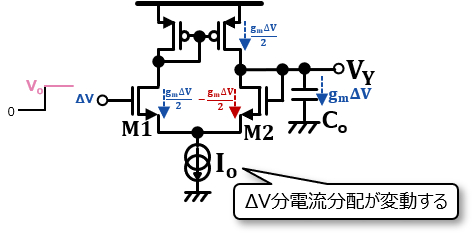

入力がΔVだけ上がると、以下のM1がgmΔV/2だけ電流があがって、同じ電流源が電流を引っ張るM2の電流源はgmΔV/2小さくなって、出力容量に充電される電流としてはgmΔVとなるんだね。

そして差動対で電流を奪い合っていることから、このgmは基本的にはテール電流で決まるんだね。

上記の応答では前項と同様のΔVに依存した理想的な応答を見れるわけだけど、さらに大信号の応答、つまりはVoが大きくなるとどうなるだろう?

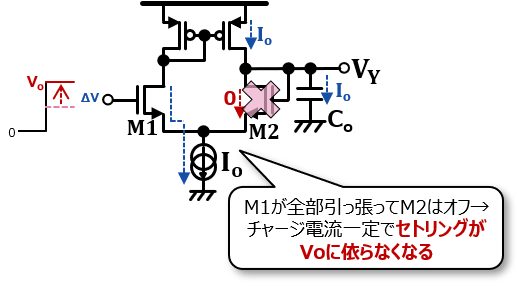

さっきも言ったけどM1とM2はテール電流を奪い合っているので、やがてはI0すべてがM1に流れていって、M2はセトリングが進んでゲートの電位があがるまではオフした状態となるんだね。

つまりはさっきまではVoを大きくするとgmΔVの電流変化があったはずが、電流がすべて片方に寄ったところで頭打ちとなって、ΔV(つまりVo)に依らなくなってしまうんだね。このセトリング特性をスルーレート特性と呼ぶよ。

次項で深掘りするよん。

スルーレート特性の応答について

では前項のような際に、応答はどう変化するかな?

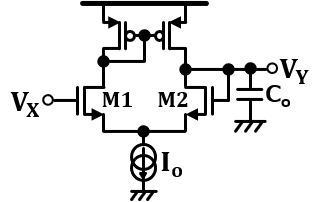

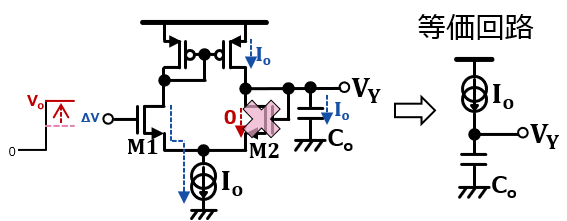

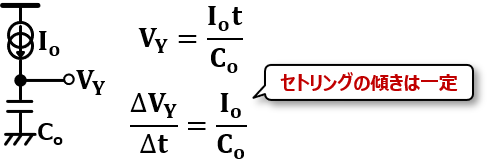

このときM2はオフしてIoがそのままCoに充電されて応答するので、以下のような等価回路で表せるんだね。

なので時間応答としてはQ=CVで今回Q=Iotのわけだから、VY=Iot/Coとなるよ。またこの際の時間変動ΔVY/Δt、すなわちセトリングの傾きはどうなるかというと、Io/Coと一定の値となるんだね。

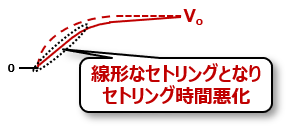

なのでセトリング応答はVoを大きくすると、以下のように最初のうちは線形の傾きとなって、理想的なセトリングよりも遅くなってしまうんだ。

じゃあスルーレートってものがわかったとして、実設計を考えたときにいろいろ疑問が出てくるかな?

ではその疑問を次項で解いて、さらに深掘りしていこう!

スルーレート特性にはどういうときになる?

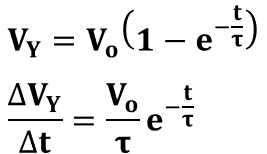

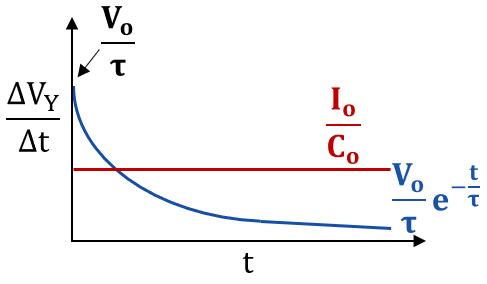

さて、理想的な電圧応答はさっき上げたけど以下のようになっていたね。ではこの時の時間変動ΔV/Δtがどうなるかな?

微分して以下のように表せたね。

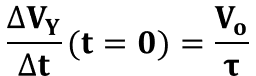

ここでさっきのスルーレート特性と異なるのは時間に依存して指数関数的に傾きが変わっていくことだね。んでスルーレートは基本的にセトリング初め(傾きが最大に部分)に出るので、ここでもt=0の傾きを見てみると、Vo/τとなるね。

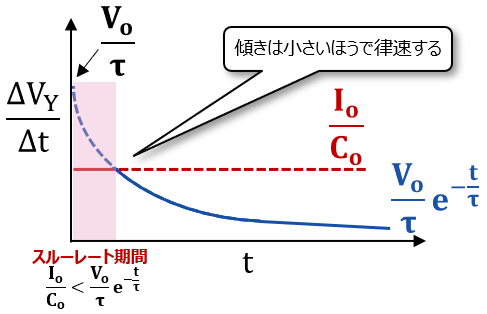

ここで、セトリングの傾きは最小に引っ張られるよ。

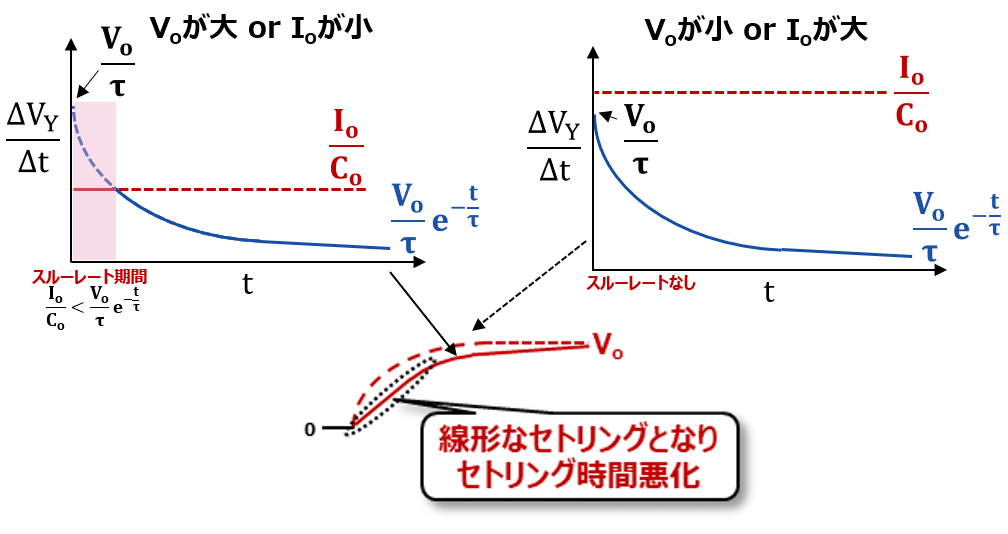

もしこのときVo/τ<Io/Coであれば、セトリングにおける最小の傾きってのがスルーレートより小さいわけだから、セトリング中にスルーレートは現れなくなるよ。逆にVo/τ>Io/Coであれば、セトリングにおいてスルーレートが現れることになるよ。

ここでの変動パラメータは当然Voであって、Voが小さい小信号の応答であればスルーレートが起こらず、Voが大きい大振幅であればスルーレート応答が出てくるようになるよ。

もちろん電流Ioを増やすことでスルーレートを防げることもできるけど、消費電流のペナルティを負うよ。また今回はユニティゲインバッファで考えたけど、実際のt=0での傾きはおよそAvVo/τと表せて、大信号応答ではスルーレートの律速を受けやすくなるよ。

オペアンプのスルーレートは以下が詳細だし、

最近はもう少し基礎寄りで以下もオペアンプについて演習から学べて分かりやすくていいと思ってる。

スルーレート特性が現れる条件でのセトリング

もう一つ重要なことを述べるよ。

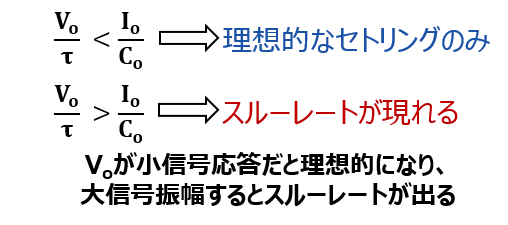

スルーレートが起こる条件の場合に、セトリングはスルーレート特性とそうでない理想的な特性が混在することになるよ。セトリングの傾きΔVY/Δtのグラフを、tをx軸と置いて描くと以下のようになるんだ。

ここで青は理想的なセトリングの傾きで、時間がたつごとに傾きは寝ていくんだね。また赤はスルーレートのセトリング特性で、時間に依らず一定となっていて、今回はVo/τ>Io/Coであることからスルーレートが起きてるよ。

また傾きは最小のところに律速するので、以下のようにセトリング初期段階ではスルーレートにて傾きが律速されていて、セトリングが進んで(Vo/τ)*exp(-t/τ)<Io/Coとなった際に初めて理想的なセトリングの傾きに戻るんだ。

つまり、理想特性の最も傾きが大きい時点は逃していることから、セトリングが理想よりもずっと遅くなることは容易に想像できるよね。

まとめると以下のようになっているよ。

他のスルーレートの例

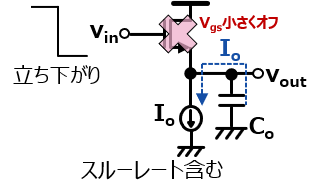

おまけだけど、差動対だと電流の取り合いでスルーレートが起こりうることがわかったね。他にもスルーレートが起こりうるケースがあって、例えばソースフォロワ。

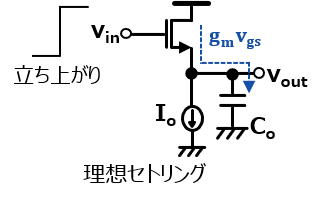

立ち上がりだと以下のように、ΔVの分だけ出力容量に流れる電流はgmvgsだけおよそ大きくなって、セトリングが進むと出力ノードの電位があがっていってVgsが小さくなっていき、セトリングの傾きが小さくなっていくと、これは理想通り。

これが立ち下がりのセトリングになると、ソースの電位が下がっていないのにゲートの電位が下がるわけで、入力デバイスはほぼオフして、入力に依存せずセトリングはIoで律速してしまうんだ。つまりスルーレート特性が出得る。

オペアンプのような差動対だと電流の取り合いのため、立ち上がりも立ち上がりも応答は同じと考えていいと思うんだけど(オフセットとか考慮しなければ)、この例では入力の極性で応答が大きく変わる可能性があるんだ。

ソースフォロワについてはここで話してるよん。

→ソースフォロワについて

今日はここまで、ほな。

雑談枠

さわざわはゲームハードでいうと64世代なんだけど(ちなみに同世代でやってる人は少なかったような、、)、64のコントローラーを持ちすぎて手が変な形で固まったことがある。3Dスティックを持つと超アンバランスな持ち方になるんよな。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–