どうも、さわざわです。

今回はデバイスの話、特に固有利得についてメインで触れていこうと思うよ。ゲインの話をすると基本単位が固有利得であることが多くて、カスコード回路の回でも出てきたけど固有利得が高いほど全体のゲインってのも大きくなるんだよね。なので固有利得って結構重要。みんなも勉強していってねい。

この記事を読めば、固有利得についてパラメータ調整の観点から理解を深めることでき、周波数応答を含めて最適な固有利得の設定のヒントとなります。

相互コンダクタンスgmの話

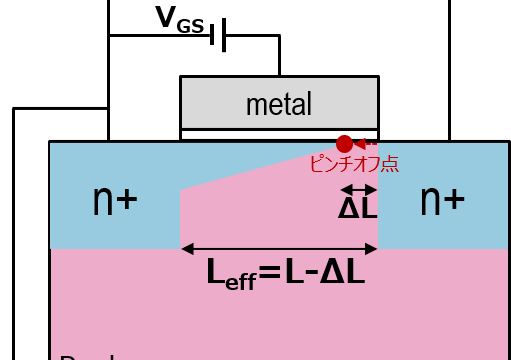

固有利得はgmroで表せたね。まずはgmの話。トランジスタは電圧を電流に変換するデバイスであって、gmってのはその変換能力を示すものだったね。つまり大きいほどVgsの変動に対してIdsの変動が大きくなる。

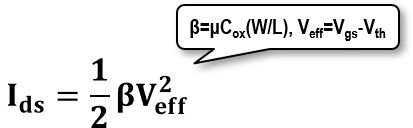

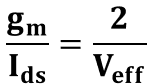

式にすると以下のようになるね。何を一定とするかでいろいろ表し方にバリエーションがあるのが重要だよ。

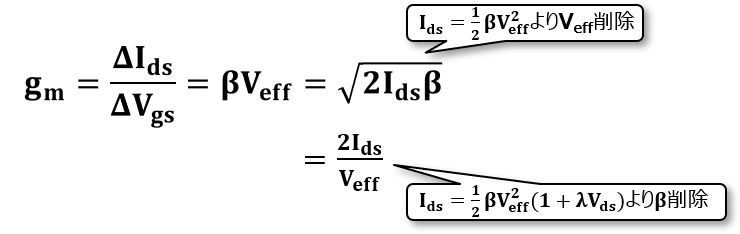

ここでVeffってのもオーバードライブ電圧っていう重要なパラメータで、さっきのgmの式から変形して、以下のようになるよね。

これは”gm over id”なんて呼ばれる回路設計でよく用いられるパラメータ関係で、ようはデバイスサイズが一定だった際にVeffとIdsを定めたらgmが決まる、例えばVeff=0.2V、Ids=1uAとかで駆動するとしたらgm=10uSってことがわかるね。

出力抵抗roの話

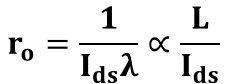

roのデバイス的な意味や式導出は、以前にチャネル長変調効果と出力抵抗の記事にまとめてるのでこっちを参照にしてみてね。ここでは式だけピックアップするよ。

→チャネル長変調効果と出力抵抗について

固有利得gmroのパラメータ依存

じゃあ前項までをもとに、固有利得をだそっか。といっても代入するだけで、電流に依存するgmをroを代入すると以下のようになるね。ここでroはLの逆数に比例するので、比例の関係で以下のようにgmroを書き換えられるよ。

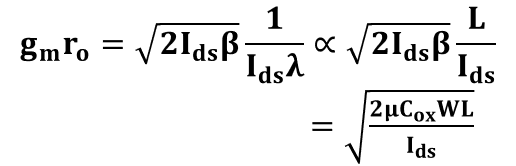

これって何を言ってるかをまとめると、固有利得を大きくしたければWでもLでもサイズを大きくすればgmroはそれぞれ平方根で大きくなるし、Idsを小さくすると平方根で大きくなるんだね。gmはIdsが大きいと大きくなるのになんだか不思議だね。以下のようなグラフになって、横軸をlog(Ids)にしておくと、-0.5の傾きでゲインが減少し行くことがわかるね。

こういったデバイス単体から固有利得の話はどこの教科書にも良く載ってるけど以下から覗いてみるのがとっつきやすいと思うよ。特にrazaviのほうは演習で手を動かして理解できていいかなって思ってる。

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

じゃあ電流を減らせばいい?周波数応答を考えよう

なんか言いたそうだね?

それは半分くらい正解なんだけど、電流をケチっちゃうと周波数応答は悪くなっちゃうんだ。そのトレードオフについて考えよう。

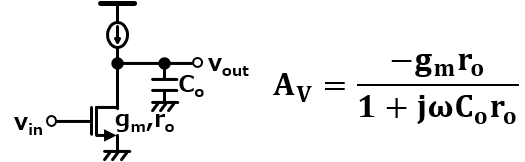

固有利得がdcゲインのソース接地回路の伝達関数って、以下のように表せるね。周波数応答の話は以前に詳しく述べてるよ!

→ソース接地回路について_小信号等価回路で伝達関数と周波数応答を出そう編

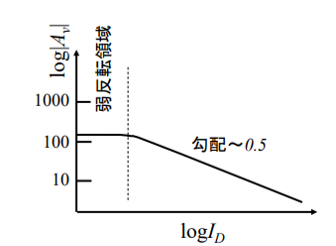

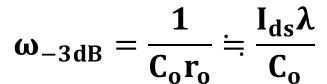

んで、この時のゲインが下がり始めるカットオフ周波数ω-3dBって第1ポールである出力ノードだとすると以下のように表せて、出力抵抗の逆数に比例する、つまりはIdsに比例するような形になるね。

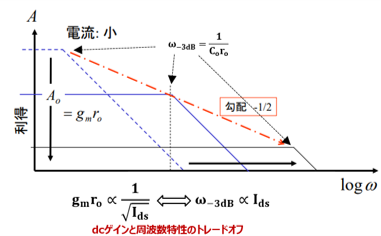

グラフで以下のように表すとわかりやすくて、確かに電流を下げると√に比例してdcゲインは高くなるんだけど、カットオフ周波数は√でなく線形に比例して小さくなるため、帯域がかなり狭まって周波数応答は悪化するんだ。

なのでただ電流を下げるといいってことは言えなくて、周波数応答も考慮して適切に電流設定をする必要があるっていえるよ!

今日はここまで、ほな。

雑談枠

串カツ田中のポテサラって中毒になるような旨味だと思ってる。串カツ食べたいってそんなならないんだけど、串カツ田中のポテサラ食べたいってなって、行くことが多いような。でもアスパラガスも毎回食べるくらい好き。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。