どうも、さわざわです。

今回はカスコード回路について触れていこうと思うよ。前回はカスコード回路について、dcゲインを上げるその凄みについて触れていったので、今回は周波数応答におけるカスコード回路の強みについて説明していくよ。一方でカスコード回路を用いる際のデメリットもさらっと触れていくよ。前回までの記事を読んでなければよければ先に読んでみてね!

→カスコード回路について_利得に触れていく編

この記事を読めば、カスコード回路の周波数応答における強みと、カスコード回路を用いる上で注意すべき点について理解できます。

カスコード回路における周波数応答の強み

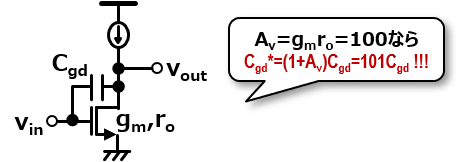

以前にミラー効果について説明したね。例えばMOSにはゲートに対してドレインとかソースに寄生容量(Cgd, Cgs)がついて、飽和状態の駆動ではCgdってCgsと比べて小さいんだけど、以下のようにミラー効果によってゲイン分だけCgdが大きく見えてしまって、100倍近く大きな容量となって周波数帯域をかなり狭めてしまうことがあるんだ。

ミラー効果についての詳細は、ぜひ過去の記事を読んでみてね!

→ミラー効果について

んで、カスコード回路はこのミラー効果も防ぐことができるんだ。それを説明していくよ。カスコード回路は以下のようになってるよね。周波数応答では理想負荷としとこう。

んで上記のようにCgdがゲイン分大きく見えてしまうのが問題なんだけど、カスコード回路ではこのXのノードはそんなにゲインがかかって揺れないことから、ミラー効果の影響は小さくなるってのが定性的な結論だよ。

んじゃあ、小信号等価回路から単純なソース接地回路との差分を定量的に見てみよう。ここで重要なのはvinからvXへの伝達ゲインだよね。相互コンダクタンスgm1は変わらないとして、ノードXでの出力抵抗っていくつになるかな。

これって以下のような回路に等価できるので、カスコードの役割のnchが負荷デバイスに見えて、ソースが動くわけだから出力抵抗にはro1、1/(gm2+gmb2)、ro2が並列に見えるから相対的に非常に大きいro*はほぼ見えず、1/(gm2+gmb2)が近似的に出力抵抗に見えるよ。なのでvinからvXへのゲインって-gm1/(gm2+gmb2)になって、nch2つのgmが同じように設計したらゲインって1倍以下になるってことだね。

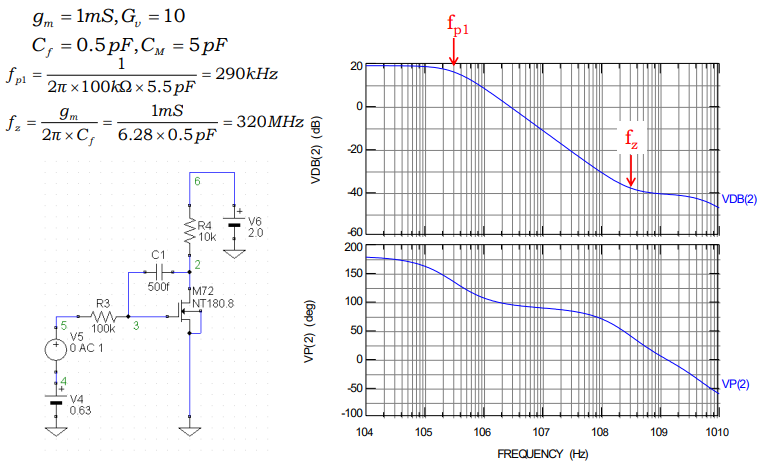

この結果、ミラー容量って2倍にもならないから、帯域制限の悪化を抑えられるんだね。実際のsim結果で比較してみると、単純なソース接地回路では第1ポールが290kHzとかなり帯域が狭くなっていることがわかるね。

これがカスコード構造にすることで、以下のように1.6MHzまで帯域を改善することができて、同じCgdでもミラー効果をかなり抑えられていることがわかるね。カスコード万歳!

上記の参考文献として以下が周波数応答の違いを視覚的にも理解しやすかったのでおすすめだよ(“はじめての”と書いている割には結構踏み込んだ内容なので初級者以外にも勉強になるかと)。

はじめてのアナログ電子回路 基本回路編 (KS理工学専門書)

カスコード回路の弱点

ゲインを稼ぎたいなら2段3段とアンプをつなげればゲインは増えるんだけど、用いる電流が増えるので消費電流がかなり増えちゃうね。それが同じ電流で実現できるからカスコードってすごいんだけど、電圧観点ではこれって弱点なんだね。まず今までのカスコードの前提って(そもそもソース接地回路とかアナログブロックの前提でもあるけど)すべてのデバイスが飽和状態で動作されていることなんだね。飽和じゃないとroとかって見えなくなるんで、大きなゲインを達成することは出来なくなるんだよね。

例えば以下のように入力と負荷でそれぞれ2段のカスコードにしていて、vb1をM1が飽和領域の境界にあるように設定し、vb2とvb3も同様に設定すると、voutがどうなるとデバイスが飽和状態から線形状態に入ってしまうだろう?

M1~M4が飽和状態で動作させるには、vdsにveff(=vgs-vth)分を確保する必要があるため、voutがveff1+veff2より下回ると、入力デバイス側が線形領域に入りdcゲインがガクッと下がってしまうんだね。同じく、voutがVDD-veff3-veff4よりも上回ると負荷デバイス側が線形に入ってしまい、同じくdcゲインがガクッと下がってしまうね。

これはカスコードデバイス無しのソース接地回路と比べると、vdd側とgnd側でそれぞれveff一個分電圧スイングが食いつぶしてしまうことになるんだ。これによって高利得で出力を大きくスイングしたくても、十分にvoutの出力レンジを確保しなくちゃいけないジレンマに苛まれて、カスコードデバイスでこのどちらも達成するには電源電圧を上げるほかないんだね。

3段のカスコードとかを用いるともっとdcゲインが得られるにも関わらずあまり用いられないんだけど、これは電源電圧があがってかえって消費電力が増加してしまうことにあるんだね。

カスコード回路はかなり有用な回路なんだけど、こういったトレードオフがあって、オペアンプもカスコード回路でdcゲインを稼ぐブロックと出力スイングを確保する段で2段構造にしたりするのがよくあるかな。

演習観点ではやっぱり以下が充実してたかな。

今日はここまで、ほな。

雑談枠

カツカレーって定期的にすごい食べたくなる。カロリ激高なものって食べたくなるもんなんだろうか。自分でカツとか作れないから食べに行くことになるんだろうけど、だいたい我慢して終わってるような。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。