どうも、さわざわです。

今回はオペアンプの特性について触れていこうと思うよ。今回の趣旨として、以前までのソース接地回路の記事からの続きとして、オペアンプの特性について解析していくので、以前の内容を読んでいない方は良かったら読んでみてねん。

オペアンプってアナログ回路の中で最も基礎的かつ難しくて奥深い分野だと思うし、さわざわもまだまだ勉強中ってところではあるんだけど、まずは伝達関数とか周波数特性とか基礎的なところから、オペアンプもソース接地回路と同様にdcゲインをかけたローパスフィルタ(LPF)であることまで説明するよん。みんなも勉強していってねい。

この記事を読めば、1段オペアンプの基礎的な伝達関数や周波数特性について理解できます。

ソース接地回路からオペアンプを考える

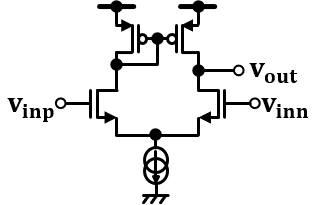

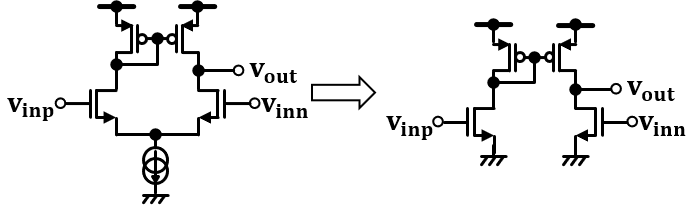

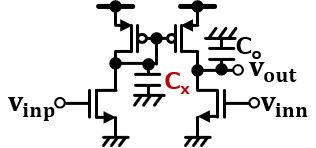

今回は以下のような1段オペアンプについて考えていくよ。ただ今回はテイル電流を理想的な定電流源として考えて、右のように全く揺れないgndと等価して考えよう。実際にはテイル電流は有限なインピーダンスをもって、同相信号を考える必要が出てくるんだけど、これは後々差動増幅回路を深掘りするときに記事にしていこうと思うよ。

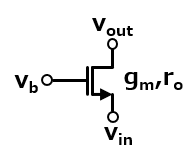

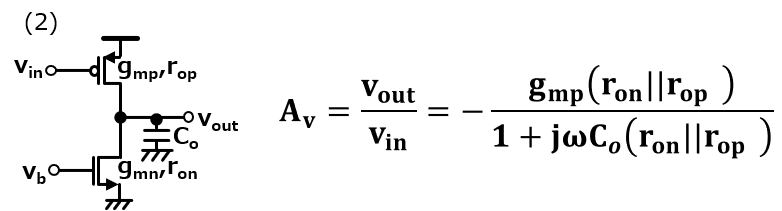

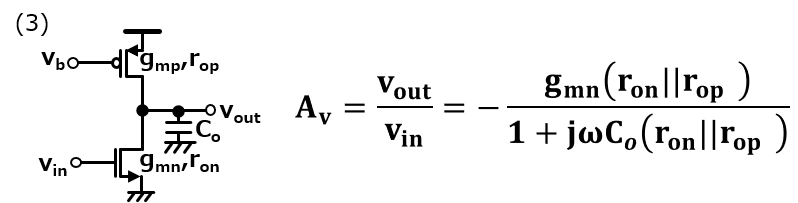

まずは復習がてらウォームアップ。上の等価回路って、以下3つのソース接地回路から構成されていることがわかるかな。これは前回までに周波数特性を含めた伝達関数を出していたけど、復習してみてね。答えは以下のようになっていたね。

前回までの記事→

ソース接地回路について_小信号等価回路で伝達関数と周波数応答を出そう編

ソース接地回路について_いろいろなソース接地回路に触れよう編

鳳テブナンの定理を用いた伝達関数の算出

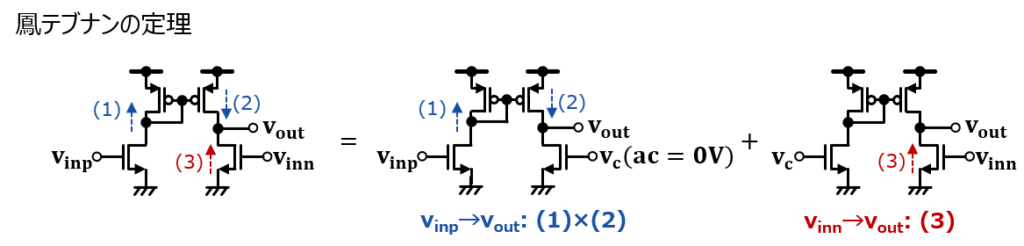

オペアンプは今までのソース接地回路と異なって、2入力1出力の回路構成になっているね。どちらの入力も出力に寄与するわけだけど、こういう時の計算に鳳テブナンの定理を用いるよ。これは、片方の入力~出力の伝達関数を出す際に、もう片方の入力は定電圧が入ってると仮定して、二つの伝達関数の和が最終的な回路全体の伝達関数特性になるんだ。

なので今回、vinp~voutを出す際はvinnはac電圧0Vとして扱って、伝達関数は上記で出した(1)のソース接地回路の後に(2)のソース接地回路が入ってvoutに出ていくわけだから、伝達関数は(1)×(2)で表せるんだ。対してvinn~voutを出す際はvinpはac電圧0Vとして扱って、伝達関数は(3)で表せる。最終的なvoutはその2通りの和で、(1)×(2)+(3)で表せることになるよ。

ではvoutの式はvinnとvinpを用いてどう表せるか考えてみて。

オペアンプの周波数応答の解析

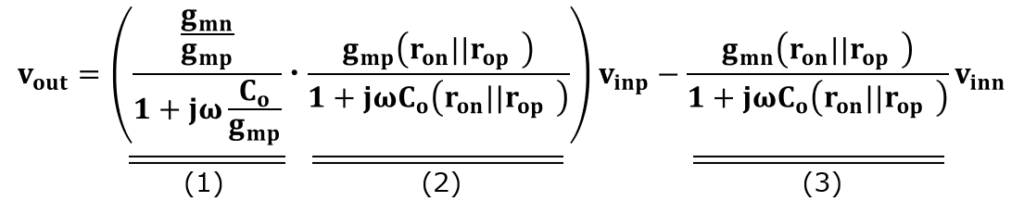

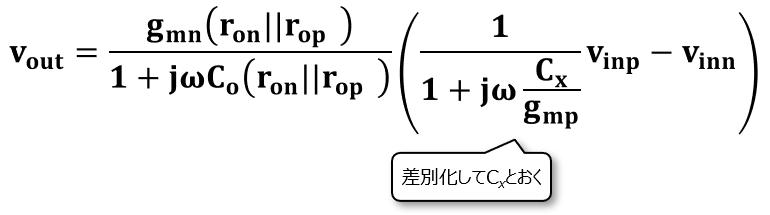

答えは以下のようになったね。共通項でくくると、右のようになるね。

ただこの時、vinpにかかっている容量なんだけど、これはvinpの初段の出力容量であって、これは重要な寄生容量なのでCxとして差別化しておこう。回路図でいうと以下の部分になるね。

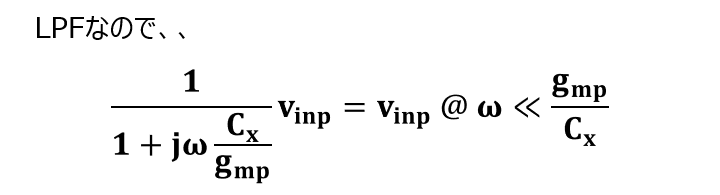

このとき、vinnに対してvinpは1次LPFにかかっているから差動回路として動作しないんだけど、ω<<gmp/Cxの条件においてはLPFの帯域にかからないためvinpがそのまま出てくることになるね。

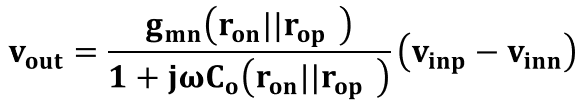

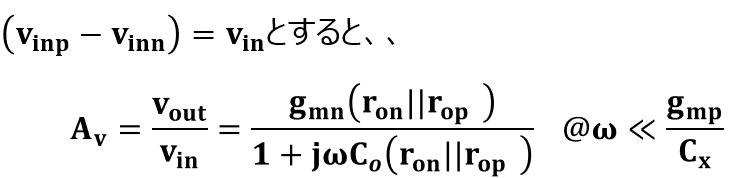

つまりこの周波数帯域で動作させる場合に限って、voutは以下のように表せて、vinp-vinnをvinとすると、伝達関数はソース接地回路となんら変わらないdcゲインのかかった一次LPFであることがわかるね。

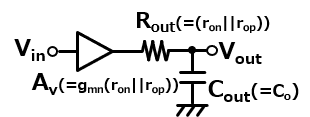

等価回路は以下のようになってるね。

ミラー極について

ここで重要なのはw<<gmp/Cxから外れるとvinpにかかる周波数応答を考慮する必要が出てくるため、差動的な応答から離れてくるよ。

この周波数帯を広めるにはCxを小さくするかgmpを大きくするほかなく、このCxがついているノードをミラー極って呼ぶよ。特にこのノードはpch2つのゲート容量がついたり、nchのCgdもミラー効果込みでついたりするから、容量が大きくなってしまって、この構造で容量を増やさずにgmpを上げるには電流を増やして駆動させるほかないから、なかなか大変なんだね。

ミラー極ができるのはカレントミラー構造を用いてシングルエンドとしているからで、例えば完全差動のオペアンプの場合(入力2に対して出力2のオペアンプ)は、ミラー極によって帯域が狭まることは防げるんだね。

オペアンプについてはまだまだ深掘りする内容が盛りだくさんだし、今後も関連記事を増やしていければと思うよ。

今日はここまで、ほな。

雑談枠

実は8,9か月前からダイエットしてて、8kgくらい減ったからダイエットとしては良いペースなのかも。一番やせたことを実感するのは、いつも使ってるベルトのとめる穴の位置が手前になっていくことなんだけど、最近はちょうどいい位置がないのでちょっと緩いくらいで止めて、ときたまずり落ちてくるのを実感してる。もう少し痩せてもう一つ内側がちょうどいい位置にせねば(←穴で止めないベルトに変えろ)。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。