どうも、さわざわです。

今日はいろいろなソース接地回路について触れていこうと思うよ。ソース接地回路って言っても入力デバイスや負荷デバイスが異なることでゲインだったり出力抵抗が変わってくるので、若干特性が変わってくるよ。ただローパスフィルタ(LPF)ってくくりとしては考え方は同じなので、ぜひ勉強していってねい。そしてオペアンプへの考え方につなげていければと考えているよ。

この記事を読めば、様々な種類のソース接地回路について、伝達関数からゲインや周波数特性の理解ができます。また負荷デバイスとゲインの関係についても理解できます。

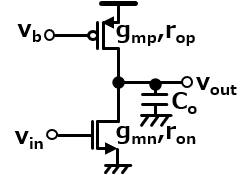

pchダイオードを負荷にしたソース接地回路

まず、以前に扱ったことがあるけど、nch入力で負荷デバイスにpchダイオードを用いたものだね。これは小信号等価回路の出し方や伝達関数の計算とかはこの前の記事に詳しく書いてるので、気になったら先に見てみてね。

→ソース接地回路について_小信号等価回路を理解しよう編

→ソース接地回路について_小信号等価回路で伝達関数と周波数応答を出そう編

このソース接地回路の特徴としては、dcゲインがpchとnchのgmの比になっていて同じ電流で駆動されていることから、pchとnchのサイズ比でゲインが決められることだね。入力デバイスで入力電圧を電流に変換する際には電流に対してvgsが2乗の特性があることから、gmは非線形を持つんだけど、出力で(負荷デバイスで)電流を電圧に変換する際にも負荷にgmを用いていることから、非線形同士で打ち消しあって線形的な応答ができるんだ。

もちろん高ゲインを得るにはnchをかなり大きく駆動能力を高く持つ必要があるけど、これは面積や寄生容量による速度とのトレードオフだったりするよ。

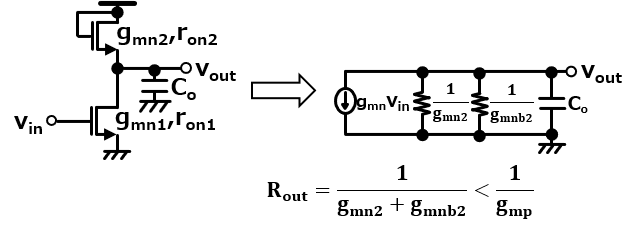

ここで復習したいのは、このソース接地回路の考え方として、以下のようにdcゲインに出力抵抗と出力容量のLPFがかかっていることと等価だってことだね。それを踏まえて他の種類の回路も見てみよう。

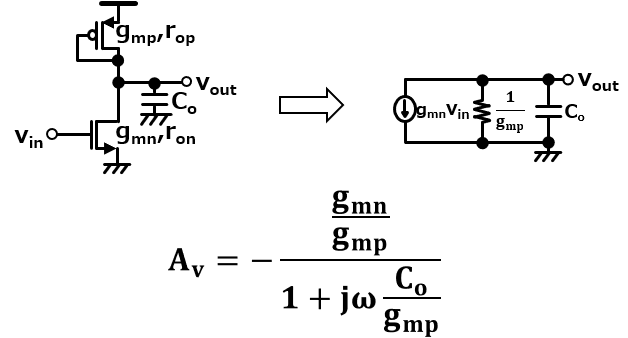

pch電流源を負荷にしたソース接地回路

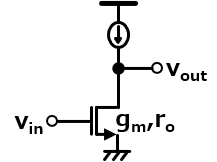

じゃあ次は以下のような、nch入力にpch負荷なのは同じで、pchゲートにdc電圧が入ってるパターンはどうなるだろう。

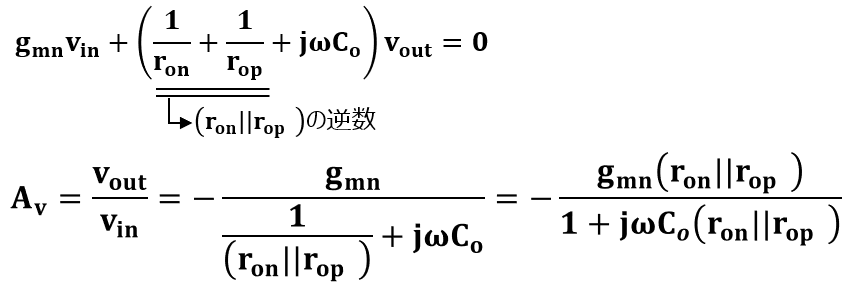

このpchってvgsのac電圧は0Vってことなので小信号等価回路で見えてくるのはropだけになるね。小信号等価回路はどう表せるかっていうと、

ってなるね。

ここでの特徴は負荷デバイスに1/gmの負荷が見えないことで、Routにroが見えてくることだね。つまり、1/gmよりはるかに大きな抵抗であるroが出力抵抗に見えることで、小信号利得を大きく持てるってことだね。仮にron=rop=roだった場合はRout=ro/2でdcゲインは

-gmro/2ってこと。ここで何か疑問に思った人は、後半を待ってねん。

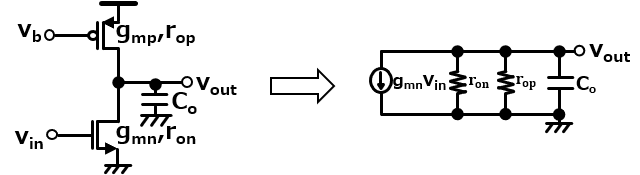

nch電流源を負荷にしたソース接地回路

次にもう一つ行こっか。これは考えるまでもないかな?

おお、そうだね!

これはRout=(ron||rop)で変わらないから入力の相互コンダクタンスだけがpchとnchで違いが出て、伝達関数は以下のようになるね。ちなみにgmは一般的にgmnのほうが大きくなるよ。その心は移動度が単純にnchのほうが大きいからだね(差分はプロセスによる気はするけど大体nchはpchの2-3倍くらい?)。

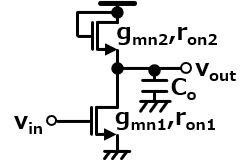

ちなみに余談になるけど、pchとnchでの違いでもう一個例題だよ。以下はnch入力にnchダイオードを負荷にしたもので、pchダイオードを負荷にした場合とどう違うかな?

pchダイオードの場合ってソースがac信号ではなかったからvbsが見えることってなかったけど、nchダイオードの場合はソースがvoutだかた小信号にvbsがでてくることになるねい。基板バイアス効果の考え方は前回のソースフォロワで述べてるので、よかったら見てみてね。

→ソースフォロワについて

そうなると小信号等価回路は以下のようになって、gmpよりgmnのほうが値が大きいことに加えてgmnb2も負荷に見えることからnchのほうがpchダイオードを負荷にしたものよりRoutが小さくなることがわかるね(つまりゲインは小さくなる)。

ちなみに基板バイアス効果の原理を追うと自然ではあるかもだけど、gm単体より基板バイアス効果を含めたgmbも負荷として見えたほうが、インピーダンスは小さく見えるんだね。

負荷デバイスとゲインの考え方

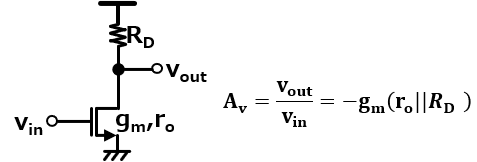

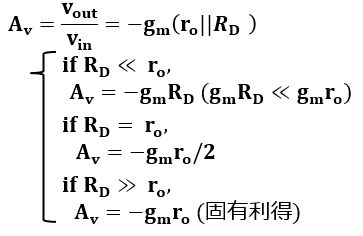

最後に以下の伝達関数を出してみて。これはソース接地回路の最もシンプルな形だけど、RDは線形抵抗で大きなはある程度変動できるとしよう。実際には線形抵抗って正確かつ大きな値にするのは向いていないんで、上ですでに示したpch負荷を用いることが一般的なんだけどね。

伝達関数はこうなるね。ここでRDがroに比べてはるかに小さいとどうなるかな。これは並列抵抗でroがほぼ見えなくなって、ゲインは-gmRDになるね。ここでRDは小さいわけだからゲインも大した値にはならないね。

次にRDがroと同じくらいだとどうなる?これは上ですでに似たようなことを言ったけど、並列抵抗でどちらの抵抗も見えていて、roの半分の出力抵抗がゲインに表れることになるね。

最後にRDがroよりはるかに大きいとどうなるかな。これは並列抵抗でRDが見えなくなるため、ゲインは固有利得の-gmroになるよ。これは負荷デバイスが定電流源であるといえて、この場合のゲインが他のケースに比べて最も大きくなることがわかるかな?

まとめるとこんな感じ。

つまり、ゲインを高めるには2つ重要なことがあって、1つは固有利得を大きくするということで、これはgmを大きくするには限界があるため、roを大きく見せることが重要になってくるよ。詳しくはカスコード回路の回に説明するね。

もう一つは大きくした固有利得をそのままゲインで取り出すために、負荷デバイスの抵抗を相対的に入力デバイスより大きく見せて、負荷デバイスを定電流源として扱えるようにするってことだね(入力デバイスと出力デバイスで、並列抵抗に見せないようにするってこと)。なので負荷デバイスには比較的長チャネルを用いるよ。

上記を意識しながら以下演習が豊富なので、いろいろ考えて見るとより理解が深まると思うよ。

次回予告

最後に次回予告。

以下にオペアンプがあるよ。この伝達関数と周波数特性を考えてみてほしい。今回は電流源が理想的で、テール電流のノードが全く動かないものとして、右のように考えてみて。そうすると、今回扱ったソース接地回路の組み合わせになってるよね。さてじゃあどう考えればいいかな。

今日はここまで、ほな。

雑談枠

ゲームセンターってもうそんなに行くことはないんだけど、さわざわはメダルゲームのプッシャーが好きだった。それこそ当時小学生くらいの頃って、貯金を使い果たして遊ぼうとしてたりしたけど、たぶん今はパチンコとかやると同じ現象が起こるかもだから、手を出さないように誓ってる。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。