どうも、さわざわです。

今回はGIDL(gate induced drain leakage)について触れていこうと思うよ。これは以前にサブスレッショルド領域におけるMOSFETを使用した際のリークについて話したけど、その際に出てきたGIDLについてもう少し深ぼった内容になるよ。みんなも勉強していってねい。

この記事を読めば、GIDLについて発生原理からどういった条件で起こりやすいかなどと、その対策を簡易的にだけ理解できます。

GIDLって何?

GIDLってのはgate induced drain leakageの略で、その名の通りゲート-ドレイン間のバイアス起因で起こるリークになるよ。以前に短チャネル効果のところで少しだけ挙げたことがあるDIBLと名前の雰囲気は似てるけど、別人の方だよ。

→微細化の凄みと短チャネル効果について

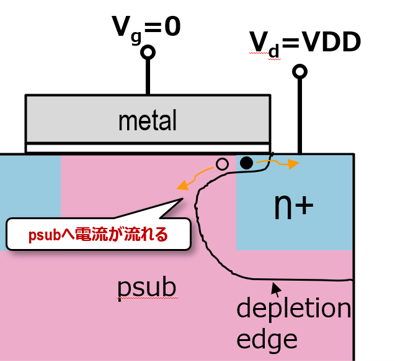

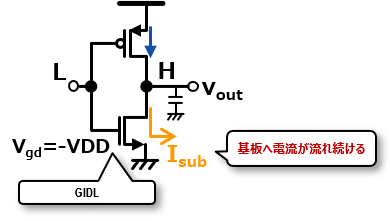

原理を説明すると、例えばゲートに0Vが印加されていて、ドレインにVDDが印加されていたとすると、Vgd(あるいはVgs)には-VDDと負にバイアスがかかっていることになるね。そうすると以下のようにゲート・ドレイン間に大きな電界がかかることで空乏層が伸びてくるよ。

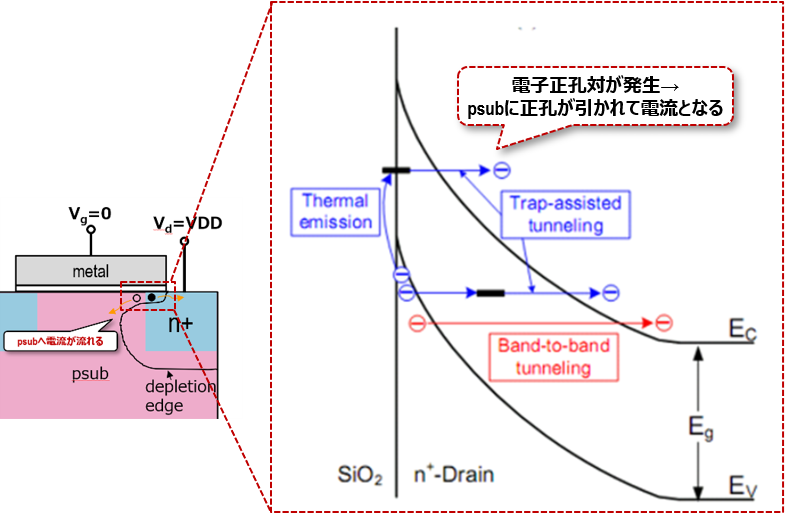

これを以下のようなバンド図で描くと、大きな負バイアスがかかることでTrap-assisted tunnelingだったりBand-to-band tunnelingだったりが起こり始めて、ドレインからの電子が基板に抜けることで電子正孔対が発生し、その分だけ正孔が基板へのリークとして電流が抜けているように見えるよ。

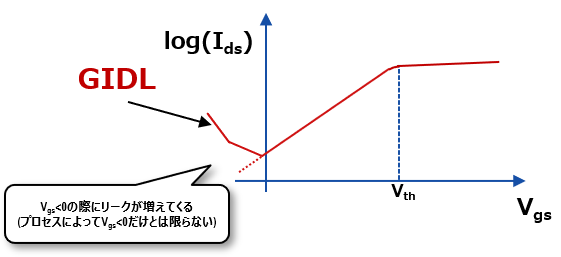

つまりはドレインからボディに電流が抜けているように見えて、以下のようにVgsやVgdが負の領域などではリーク電流が大きくなっていく現象となるよ。

ちなみにGIDLがない場合はVgsが小さくなっていくほどドレイン電流は小さくなっていくって話は、前回のサブスレッショルド領域での電流について触れているので読んでみてね!

→サブスレッショルド領域の電流について

どんなケースで悪さするか

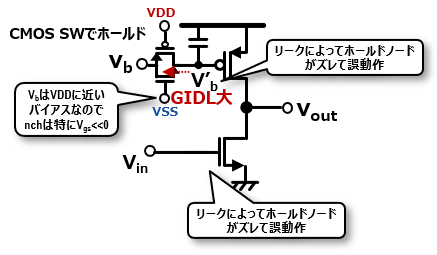

じゃあ設計においてどんなケースで悪さするかって話だけど、以前にも挙げたようにサンプリングSWを使用した際にホールド時のフローティングノードからGIDLによってリークでホールド情報が変わっていってしまうことが懸念されるよ。

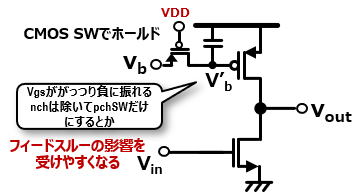

例えば↑のようにpch電流源のバイアスにサンプリングSWを用いる際に、フローティングノードはVDDに近いような電位を保持させようとするわけだけど、この際のホールド時だとnchはゲートに0Vが入って、大きな負バイアスからGIDLが現れることが考えられるよ。

高い電位を用いる前提ならpchだけのサンプリングSWにしてもいいかもだけど、サンプリングSWは別途記事を書いてみてたので読んでみてね。

→サンプリングスイッチと電流源への応用について

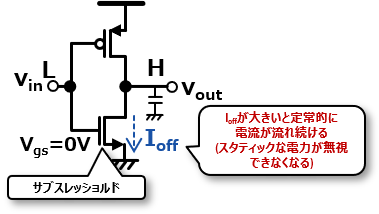

他にも前にサブスレッショルド電流の話でも言ったようにGIDLはオフリークの電流として分類されるので、単純にスタティックな電力が増加するってことも懸念されるよ。

これはインバータを考えただけでもわかりやすくて、前回述べたのは出力がHの際にnchはオフっているわけだけど、Vgs=0Vなのでサブスレッショルド電流が無視できないオーダーの際には大きな消費電力につながるんだったね。これはVthを上げたりLを長くしたりで何かしら対策しないといけないね。

一方でここでいうVgdも最初の原理でいったような負バイアスがかかっているわけなので、ドレインからボディへの電流が流れて、同じくスタティックな電力増加につながってしまうことが考えられるね。

リーク電流とひとえにいってもいろいろあって大変だぁ。。

対策一例①

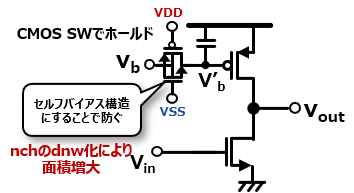

上記のサンプリングスイッチのケースにおいて、よくある対策一例だけ簡単に触れてみるよ。一つはCMOSスイッチをセルフバイアスのような構造にするってことだね。

ボディが固定されている際にゲートとドレインの電位が負の方向に離れていくと空乏層が生じてさっきのようなリークが出てたわけだけど、セルフバイアスにすることでドレインにあわせてボディも動かせば前述したような空乏層も生じにくく、GIDLが起こりにくくなるっていえるかな。

ただこれはnchをセルフバイアス構造にする、つまりはdeep n-well構造にしないといけないってことになるので、面積が大きくなっちゃうよ。ここについては以前にソースフォロワで簡潔には触れているよ。

→ソースフォロワについて

あとはリーク経路をちゃんと理解して、例えばnch起因のGIDLが支配的なのであればpchだけを使ったサンプリングスイッチにするとか、その際にはフィードスルーも別途pchを入れて対策が必要かもだけど。

GIDLが悪化する条件

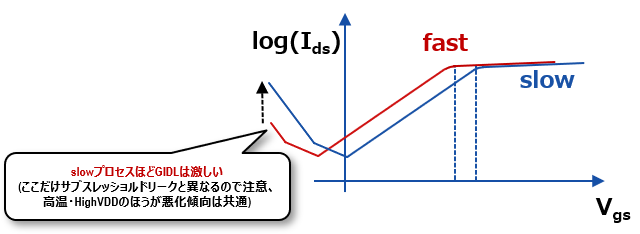

ちなみにGIDLがどういった条件でワーストなのかって話だけど、基本的にはサブスレッショルドリークだけでなくトンネリングを基にしたこのGIDLも、温度が高いほどリークが顕著になってくるよ。

まあ温度は予想通りなんだと思うんだけど、もう一つはプロセスばらつきで、これはドーピング濃度が高いほど空乏層が伸びにくくなるので、ゲート・ドレイン間にかかる電界が大きくなって、トンネリングが起こりやすくなるんだね。

つまりはVthが高くなるslow条件のほうが一般的にはGIDLが起こりやすいとされているみたい。ここはオフリークと違うので注意が必要だよ。

なのでいずれにしても重要なのは、サンプリングスイッチを使用するケースにせよフローティングノードは注視して設計しないとってことだよね。

対策一例②

そもそもの根本原因は上記したようなデバイス起因の現象なので、回路設計者にできる対策ってのはあんまりないように思えるよ。ってことで元も子もないことを言うと、プロセスを変えてGIDLが悪くないような素子を使用するってことが根本として挙げられるよ(プロセスによってGIDL特性はだいぶ違うらしく、プロセスを変えた際の不具合の一因にもなり得りそうな)。

例えばFDSOIとかってのは原理的にボディに電流が抜けにくい構造になっていると思うので(そんなことないんかね?)、これによりGIDLって起こりにくいのかなって感じはするし、ゲートとドレインのオーバーラップが小さい素子の場合にもGIDLは起きにくいわけなので、、。

なので設計観点でできるのは素子プロパティをよく理解するってことぐらいか?いずれにしても初プロセスを使用する際にはこういった情報を正しく理解するのは重要だよね(あとはモデル化されてるかとか)。

ちなみにさわざわは全く詳しくないんだけど、NANDフラッシュメモリとかを微細化していく際にこのGIDLを利用して書き込みを行うとかってのがあるみたいで、鋏は使いようなんだね。

今日はここまで、ほな。

雑談枠

ギデュギデュ^^。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。