どうも、さわざわです。

今回はサンプリングスイッチについて触れていこうと思うよ。以前に挙げたS/H回路でも用いられるものだけど、サンプリングスイッチ単体でもアンプの電流源とかに良く用いられるように多岐にわたって応用される回路なので、前回軽く触れたチャージインジェクションやクロックフィードスルーも含めて触れていくので、みんなも勉強していってねい。

この記事を読めば、サンプリングスイッチ回路についてフィードスルーを含めて基礎的な部分と、電流源に応用する恩恵とかも理解できます。

サンプリングスイッチとは

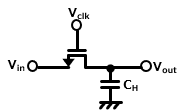

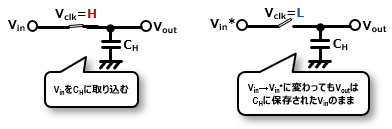

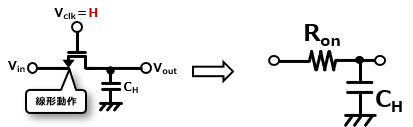

サンプリングスイッチってのは以下のような単純な回路で、nchがオンしているときはサンプル期間で入力信号を出力が追従していて、nchがオフした時点でホールド期間に入って出力がその時点のノードで決まる。

ちなみにこの際nchはVdsがほぼ生まれないことから線形動作をしていて、サンプルする際の時定数ってRon*CHで決まることになるね(あとはVinがVclk-Vth超えるとオフするね)。

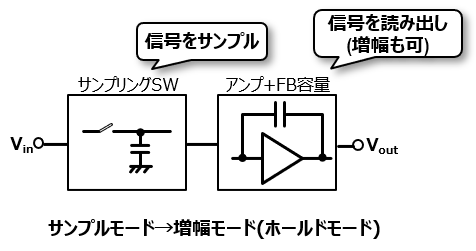

これによって信号の保存が可能で、アナログ回路にて多岐にわたって用いられてる技術だよ。主には読み出しも含めてアンプと組み合わせて帰還技術を用いてスイッチトキャパシタアンプのようなS/H回路のように用いられたりするね(このスイッチ単体だけでS/Hとして用いることもできると思うけど)。

→スイッチトキャパシタアンプのサンプル・ホールドについて

これのディジタル値だったらメモリと同じなんだけど、アナログ回路においては保存されたノードの精度が高くないといけない場合が多いので(ADCとかで)、この際のノイズとか精度悪化につながる要因はよく抑えなきゃいけないってことで、次項に行くよ。

フィードスルーについて

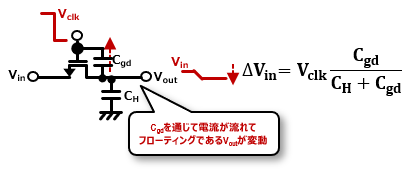

ここで入力信号の他にゲートが動いてサンプルとホールド期間を切り替えているので、このダイナミックな電圧変動はCgdを介してホールド期間でフローティングとなったノードにアタックするね。これをクロックフィードスルーと呼ぶよ。

↑のフローティングになったホールドノードに対する変動ってのはクロックの振幅とカップリング容量とホールド容量によって決まるよ。

ただしnchがオフるまではホールドノードはフローティングになっていないため、バイアスによって変動を戻す力が働くことで、↑の変動を表してる式はワースト条件っていえるのかな。

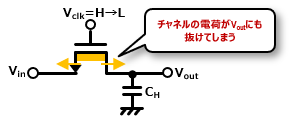

あとはチャージインジェクション。これはMOSスイッチをオンからオフにする際に、チャネルに居た電荷が一部フローティングノードに流れてしまって誤差となる現象だよ。

今回は詳しくは割愛するけど、上記のフィードスルーやチャージインジェクションは別途キャンセル用のスイッチをつけることでキャンセルできるよ。

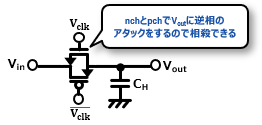

例えばNMOSスイッチではなくて、以下のようなPMOSも加えたCMOSスイッチにしとくことで、チャージインジェクションは電子と正孔で補えるし(nchが出した電子がpchに流れるイメージかね)、Vclkは逆相であることから変動は相殺できるよね。

nchとpchのプロパティは考えないとだし、完全にキャンセルし切るのは難しい気もするけど。

上記を含めたフィードスルーはS/H回路でも無視できないノイズとして現れるので、対策として読み出し方にいろいろと工夫があったりするよ。

→スイッチトキャパシタアンプのサンプル・ホールドについて

サンプリングする際に乗るdcノイズ

ここでサンプリングスイッチのような方式ではサンプリング時に取り入れたい信号だけでなく、必ずノイズも含めてサンプリングされてしまうよ。

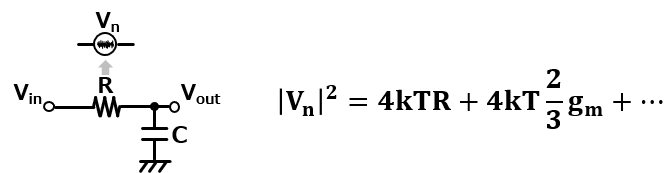

これは以下のようにサンプルのSWが抵抗成分として見れるので、これがノイズ源となると。さらにはこの抵抗はこのSWだけでなく例えば前段の抵抗成分なども含めてトータルで見えることに注意だね。

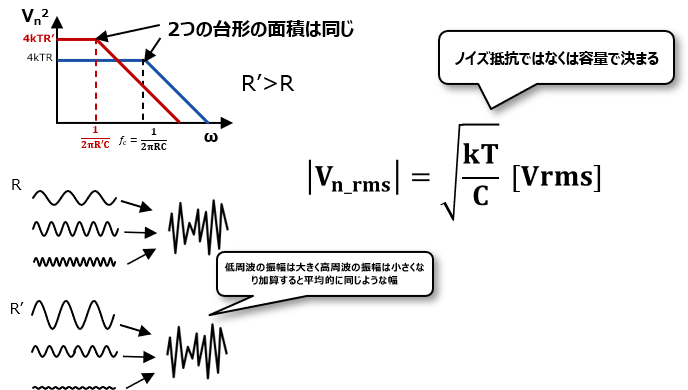

こっからの詳しい計算や深ぼった話は以前の記事に譲るけど、このノイズを評価する際には抵抗の大きさでは決まらず、容量成分、つまりはサンプリング容量によって決まることになるよ。

→kT/Cノイズとノイズ帯域幅について

これをkTCノイズと呼ぶけど、ノイズを減らすには容量を大きくするほかないけど、容量を大きくすると面積だけでなくサンプルにかかる時定数を大きくなってしまうことから、このノイズはなかなかの曲者なんだね。

サンプリング後はdc的なノイズ(オフセット電圧)として保存されてしまうので、後々フィルタなどで信号と分けて取り除くのが難しくなるって観点でも。

電流源でのサンプルホールドの活用

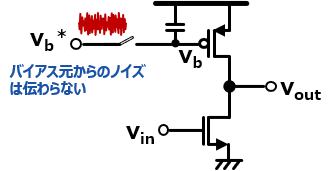

一方で電流源としてサンプルホールドを用いると、ノイズに強くなるケースもあるよ。

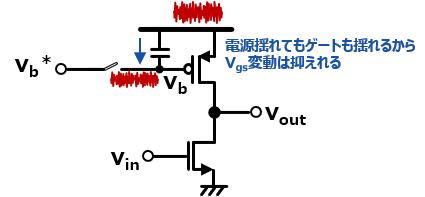

例えば以下のように定電流源を作ることを考えると、所望のバイアスでホールドできればその後に供給元からノイズが乗っていても電流として出ることはなくなるよね。

後は電源電圧が揺れてもCHを通じてホールドノードが同相に揺れることからVgsが変動しにくく、電流として現れにくくなるよ。これによって低周波のさPSRRとかはよくできたりとかがあるけど、フィードスルーによる変動やPSRRの特性も含めてCHの大きさを決めたりってなるのかな。

(ちゃんと検討とかしたことのないちょっとした疑問だけど、高周波になるとpch電流源のソースでのPSRRの揺れとゲートでの伝達に遅延が出てきて、高周波領域ではむしろサンプル・ホールド方式がPSRRは悪くなるんかね。おそらく出力の帯域でカットされちゃうような周波数領域なんだと思うけど)

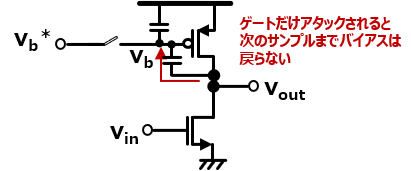

一方でホールド中にひとたびゲートがアタックされると、HiZであることから電位が変動して戻らなくなるので、単純に良いことだけってわけではないことには注意が必要だよ。

今日はここまで、ほな。

雑談枠

セブンのゴロッゴロにフルーツ入ったヨーグルトを毎日食べられる人間になりてぇ~。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。