どうも、さわざわです。

今回はポールスプリットについて、小信号等価回路観点からの解析とゼロ点の影響について触れていこうと思うよ。前回からの続きでポールスプリットの概念的なことを説明したけど、実際にはポールがどうなるのかってことを伝達関数を出してみてみよう。するとおのずとゼロ点のケアが考慮に入ってくることがわかるかな。みんなも勉強していってねい。

この記事を読めば、ポールスプリットを小信号等価回路の観点で理解できます。またポールスプリットを用いた際のゼロ点のケアについてもわかります。

前回までの復習

前回までの復習だけど、2段オペアンプは各段の出力のポールが近くdcゲインも大きいことから、ネガティブフィードバック(NFB)を用いると非常に不安定になりやすいんだったね。

これに対して安定化設計する手法の一つとして、ポールスプリットをすることで二つのポールを引き離すってのがあったね。

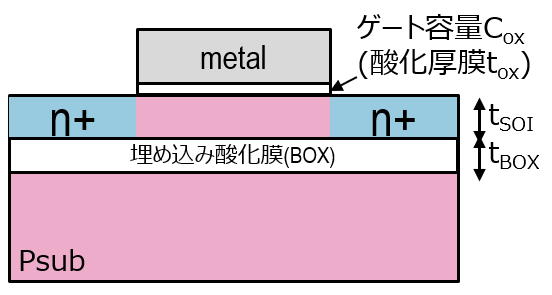

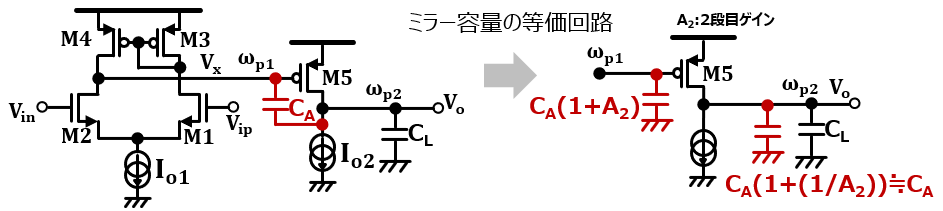

面積をできるだけかけずにポールスプリットを実現するには、以下のようにミラー容量を用いると、2段目のゲインがかかって容量が大きく見えるので、一見よさそうに見えるね。

今日はこの回路について、深ぼろう。

前回までの内容は、以下を確認してみてね(ほぼシリーズ化しとる)。

↓

ネガティブフィードバックについて

安定性設計におけるポールと位相余裕について

オペアンプの安定性と最適な位相余裕について

オペアンプの位相補償:ポールスプリットについて-基礎概念を理解しよう編-

小信号等価回路での伝達関数

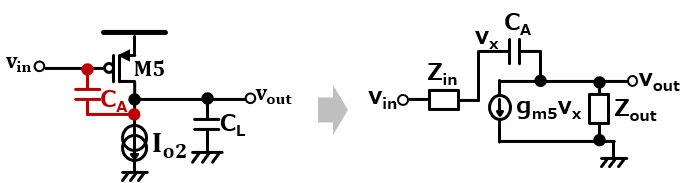

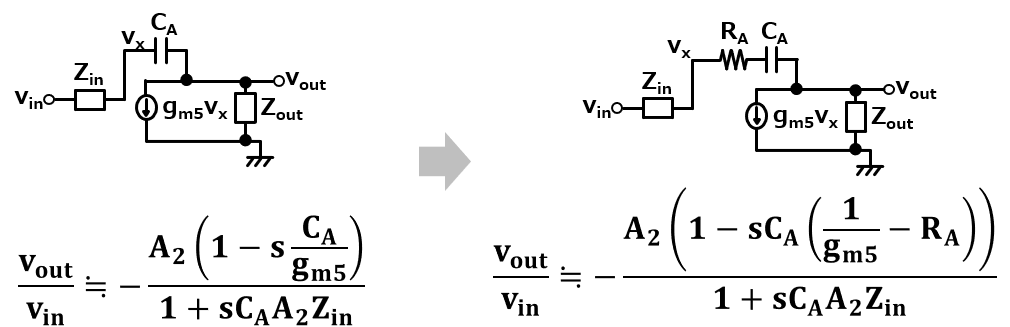

ではここからは小信号等価回路での応答を考えてみようって話で、1段目と2段目の全てのパラメータを考慮した伝達関数を計算してもいいんだけど、かなりタフな計算になってしまうので次回に譲ってここでは位相補償する2段目に着目して、以下のような回路に簡略して考えてみよう。

ここでZinは2段目入力の抵抗・容量を加味したインピーダンス、Zoutは2段目出力の抵抗・容量を加味したインピーダンスとなるよ。

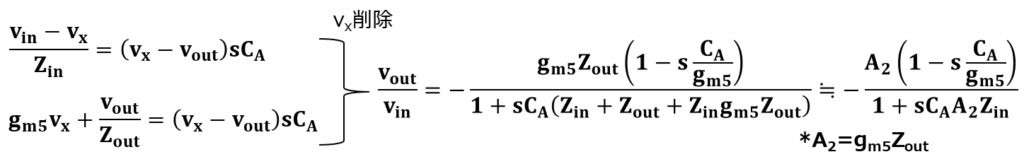

みんなも手を動かしてvinからvoutへの伝達関数を考えてみてほしいんだけど、以下につらつらと計算を書いておくよ。

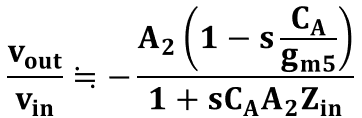

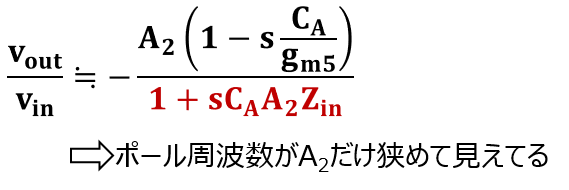

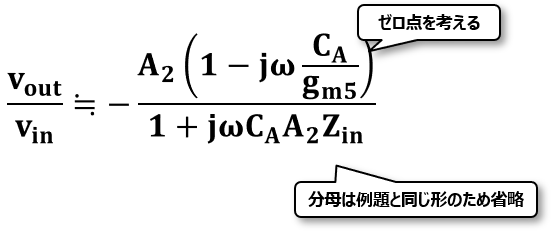

ということで最終的には↑のように計算ができたよ。ここで注目すべき点が二つあって、1つ目はこの2段目アンプのdcゲインはA2=gm5Zoutなので、分母のポールの着目した際に、確かにA2倍だけポール周波数が小さく見えていて、ミラー効果によって実効的な容量が大きく見えていることがわかるね。

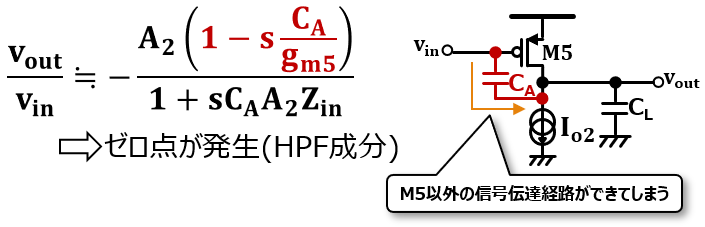

2つ目は、今度は分子のゼロ点のほうで、2段目の入出力間に容量を挟んだことから、信号の経路としては2段目の入力pchだけでなく、周波数帯によっては容量を介した経路が見えてしまうことになって、これは前回いくつか挙げたポールスプリットのやり口の中で、ミラー容量を用いたケース特有になるね。つまりはハイパスフィルタ(HPF)成分が生まれたってことになるよ。

ここではポールスプリットを用いた2段目の周波数特性を考えるための、かなり簡略化した例であることには注意が必要だよ。実際にはZinやZoutは容量成分、すなわち周波数特性をさらに考慮する必要があるので。

2段オペアンプの各ポールがどうなるかなどは、次回にもっと踏み込んで説明できればだよ。

周波数特性を考える

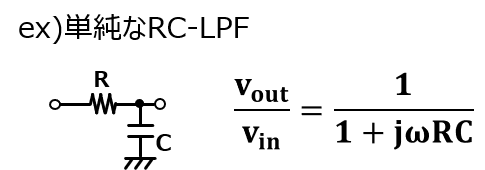

まずここで今一度このポールの役割を考えてみると、一般的なRCのローパスフィルタ(LPF)と同じで、分母の形は以下の形と似ているよね。

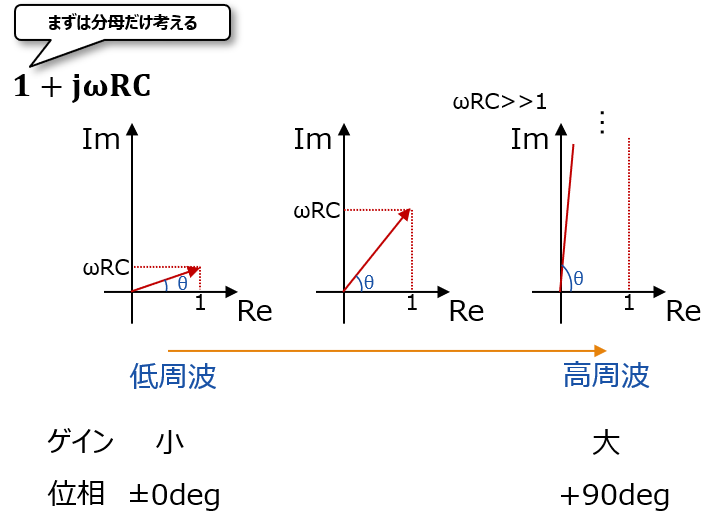

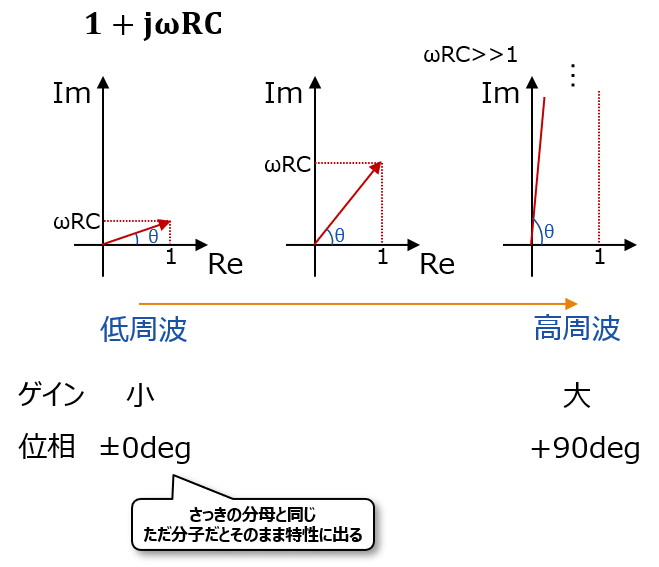

以下のように複素数で考えると、周波数が低周波から高周波になるにつれて虚数の項が支配的となってきて、位相としては+90deg回って、以下赤矢印の長さは+90degに近づくほど大きくなってくることから、伝達関数の分母の位相が+90deg回って絶対値(ここではゲインと表記)が大きくなってくることになるので、

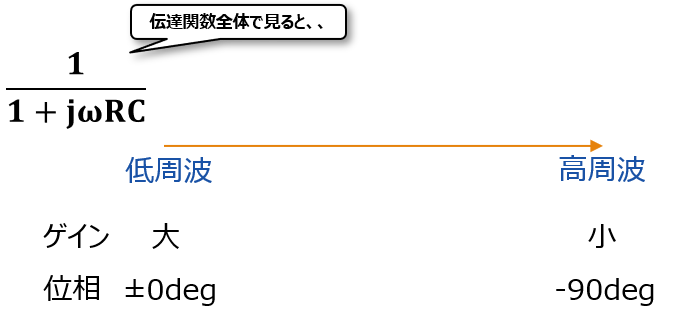

伝達関数全体で見ると位相は-90deg回ってゲインとしては小さくなってくることになるんだ。これが複素数でちゃんと考えた際のLPF特性になるんだね。

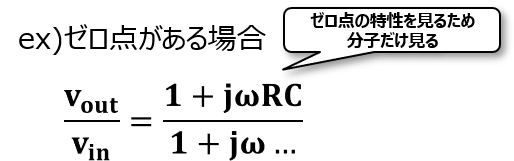

次にゼロ点。例えば以下のようなHPF成分を含む伝達関数のゼロ点を考えよう。

同じく複素数で考えると高周波になるにつれて位相は+90deg回るのは同じで絶対値が大きくなるのも同じだけど、この複素数は伝達関数の分子にいる違いがあるので、位相はそのまま+90deg回って高周波になるほどゲインは大きくなることになるよね。これがHPF特性として出てくるんだね。

じゃあ今回扱ってる伝達関数ではどうなる?

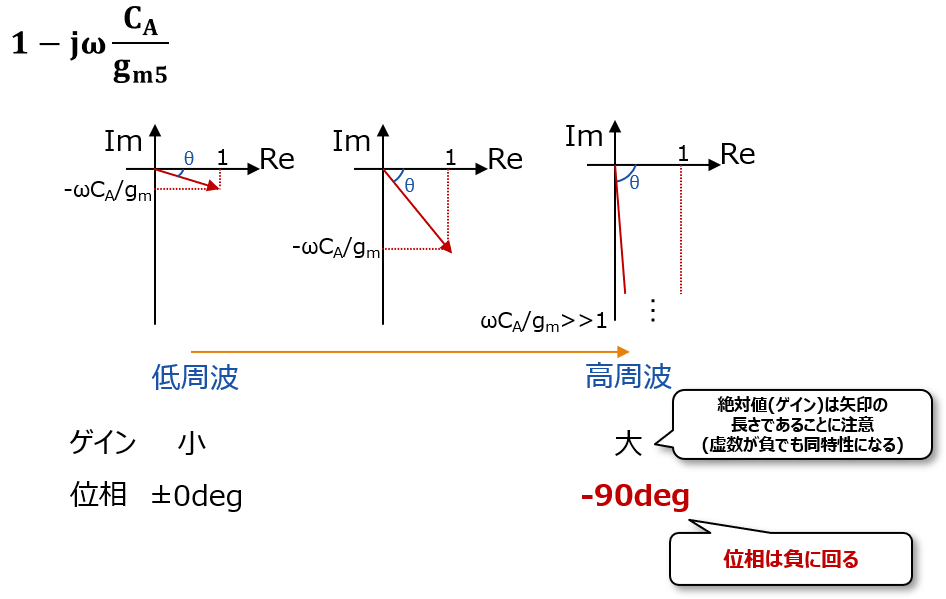

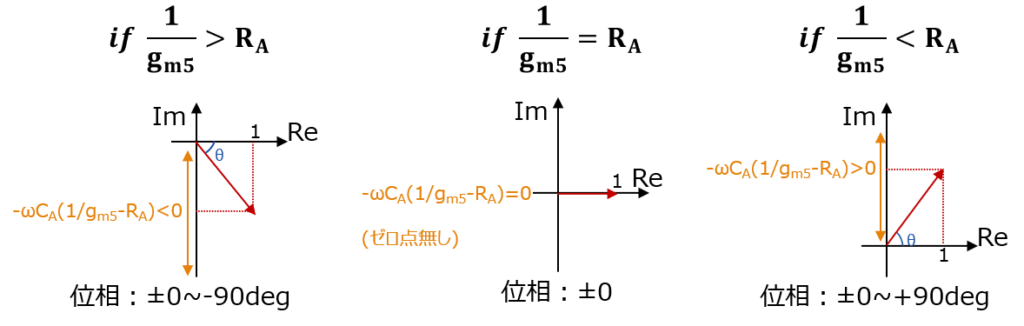

ここで重要なのは、ゼロ点の正負が上記の例とは逆になってるよね。これだと以下のように、周波数が大きくなるにつれて矢印が長くなることには違いないのでゲインは大きくなるんだけど、+90degではなく-90deg回ることになるよね。

これが位相補償においてどんなことを指すのか、察しのいい方はもう気づいているかな。

位相補償におけるゼロ点の与える影響

このゼロ点は、位相補償において最悪なんだね。

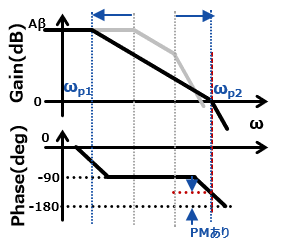

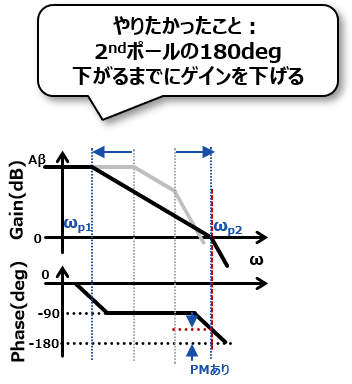

その心はもともとの位相補償の目的に立ち返ると明確で、位相補償の目的はPMを十分作ること(大体60degあたりまで)だったので、-180deg回るまでにできるだけゲインを下げて待ち構えたいと。つまりは第1ポールと第2ポールを十分広げて、第2ポールを迎えて位相が-180deg回った際までにゲインを下げるってのがポールスプリット。

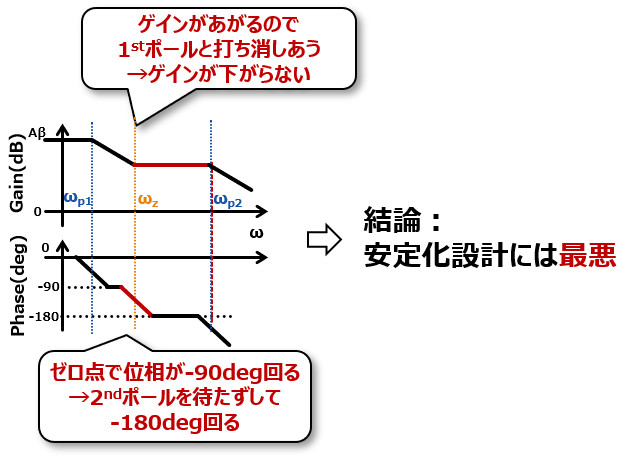

ところがここに今回のようなゼロ点が挟まると、以下のように下がっていたゲインは止まる、そして位相は第2ポールを待たずして-180deg回る、といった感じでやりたかったことと全く逆のことが起こり、当然PMを出すのが困難になる(ゼロ点周波数をωzとしている)。

これによって、ミラー容量を大きく降っていっても、一向にPMが改善しないってことが起こりえるよ。なのでこのゼロ点を何とかしないといけないって話になるよ。

ゼロ点への対策

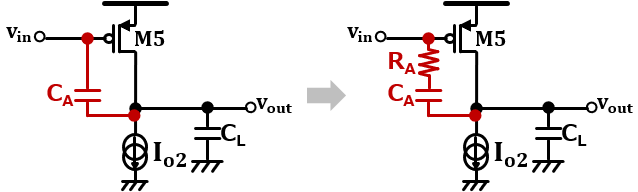

ここからは位相補償によって生まれちゃったゼロ点を消去する方法に触れていくよ。結論から言うと、以下のように補償容量と直列に抵抗を挟むってことになるんだけど、これがなんでゼロ点削除になるのか。

これはさっきの回路が下のように書き換わるんだけど、これを同じように伝達関数だしていくと以下のようになるよ。みんなも手を動かして計算してみてね(sCA→1/(RA+(1/sCA))に置き換えるだけでいけるけど)。

ポールも若干変わっているけど、今回注目すべきは分子のゼロ点の部分で、sCAにかかってる括弧内が1/gm-RAとなってるので、RA=1/gm5とすることができれば、sCAの項が消えてゼロ点がいなくなることにあるよね。

ここでRAは線形抵抗で表記されているけど、実際はトランジスタを用いて作ることが多くて、この際のバイアスの作り方などは別途機会があれば記事にまとめてみようと思うよ。

以下は結論のない余談として聞いてほしいけど、ここで疑問に思う点として、果たしてゼロ点を削除するほうがよいのかね。

ここでの選択肢として、以下のようなHPF成分は最悪だってのはもう話したね(RA<1/gm5)。んで今述べたのはRA=1/gm5にしてゼロ点をなくして、HPF成分をなくしたと。

もう一つはRA>1/gm5にすることでsCAの項を正の値にして、HPF成分の符号を変えようってのも考えられるよね。この際は複素平面で考えると↑のように、高周波になるにつれてゲインは上がるも位相は+90deg回るので、位相補償的には悪くないんじゃないかなと。

ちなみにこれに対する明確な答えはそんなに分からないというか、実際に検証してみてって感じな気はするんだけど、例えばゼロ点周波数によってはゲインが0dBのちょい上くらいを上がらず下がらずで並行して走ったりになって、不安定になりやすい周波数帯が増えて若干セトリングにヒステリシスが出るのかななんて思ったりもするけど、位相はそこまで回っていないはずなのでまあ何ともって感じ。

ただパラメータばらつきも考慮してきれいにゼロ点を消せるかは分からないし、仮にRA<1/gm5になったら一気に安定性がかけることも考慮すると、マージンをもってRA>1/gm5にしとくでもいいのかなって気はしてる。

今回の内容は以下あたりを読めば十分な理解ができると思うのでおすすめだよ。

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

Analog Integrated Circuit Design

次回予告

今までの内容を踏まえて、復習の意も込めながら次回では2段オペアンプの位相補償について、パラメータをどれくらいに調整にすればよいのかも含めてサマリ的な内容をあげるね。

今までは追加の容量の話に着目してたけど、各アンプのgmとかもかなり重要になるわけで、あとは補償後の各ポール周波数がどうなってるかとか、そこらへん含めて位相補償の内容をいったん締めようと思うよ。

今日はここまで、ほな。

雑談枠

転職したわ。前職の専門知識とか、記事にしちゃおうかしら。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。