どうも、さわざわです。

今回はボディ・ソース接続構造を使用する際のあれこれを触れていこうと思うよ。知っての通りMOSにはボディ端子がいるけど、nchはgndに、pchは電源につなげておくことが多い一方で、これをソースとショートさせて使うような方式もあるよ。これについて良し悪しを考えていこう。細かい内容である一方でアナログ回路設計特有の内容だとも思うので、みんなも勉強していってねい。

この記事を読めば、MOSFETのボディ・ソースを接続してアナログ回路設計に用いる際のメリット・デメリットについて理解できます。

ボディ・ソース接続構造とは

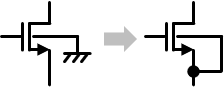

さわざわはこのボディ・ソース接続をいつからかセルフバイアスって呼んでたんだけど、一般的じゃない気がしてきたんで今回はボディ・ソース接続構造と呼ぶね(実際セルフバイアスは他のことも指していそうだし)。これは以下のようにボディ端子を、gndや電源でなくソースに接地することを指すよ(セルフバイアスであってたら教えて)。

本来ソースがgndについていないで何かしらの電位を持っている場合(nchを例にとって)、ボディをgndにつないでおくとVbsが発生して基板バイアス効果によってVthが上昇するんだね。

これをボディにソースを接続することに依ってVbsがなくなって、基板バイアス効果を抑えられるんだね。回路的にやり方としてはボディのつなげ方を変えるだけなんだけど、じゃあ以降で基板バイアス効果の影響も考慮しながら、このボディ・ソース接続構造の効果について深ぼっていこう。

ボディ・ソース接続構造の利点

ボディ・ソース接続構造を用いるメリットとしては上述したように基板バイアス効果を抑えられることになるよ。これがなんでいいのかってのを考えていこう。

まずは上述したようにソースが内部電位を持ってしまうことでVbsがかかってしまい、Vthが上昇してしまうんだね。

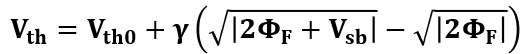

これは以下のようなnchで説明すると、もともと以下のように基板バイアス効果ってVbが負の方向に触れていくとVsbが大きくなっていき(空乏層が広くなっていくことで)、Vthがオリジナルの値(Vth0)から大きくなっていってしまうんだ。

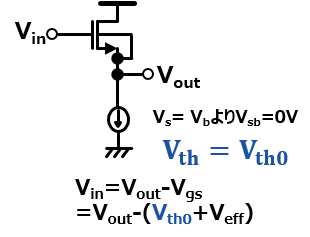

一方で、回路で見ると以下のようにソースもボディもgndにつながっているのであれば、Vsb=0Vになるわけなので基板バイアス効果は起こらず、Vth=Vth0とオリジナルのまま設計ができるんだね。

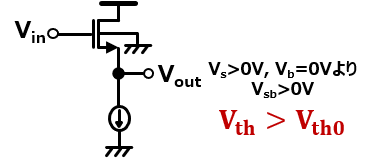

ところが以下のような回路構成になった場合に、Vsが0Vでなくgndから上昇した電位を持つことになるので、相対的にVbは負の方向の振れてることになって、Vsbの上昇により基板バイアス効果が起こってVth>Vth0となるんだね(条件やプロセスにもよるけど0.4~0.6Vとか、結構がっつりVth上がる)。

この結果何が起こるかというと、Vthが上昇したnchを駆動するためにより大きな電圧が必要となり、電源電圧を低く設定できないことが問題となるよ。

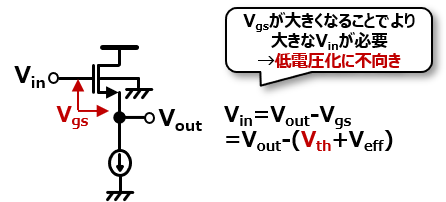

例えばソースフォロワ構造が最たる例なのかもしれないけど、ソースフォロワの出力は入力電圧からVgsだけ引かれた値が出されるよ(これは小信号ではなく大信号レベルでのお話)。

つまりはVgs=Vth+Veffであることから、Vthが大きくなることで出力部の電圧スイングが狭まってしまい、十分確保するためには入力電圧をより高いレベルに設定する必要が出てくるよ。

これをボディ・ソース接続構造にすることでVth=Vth0のまま基板バイアス効果で上昇させることなくデバイスを用いることができるため、低電圧化に向いているっていえるんだね。(もちろんVthを下げて他に特性として問題なければ)

また小信号応答観点でも出力インピーダンスが大きくなるメリットがあるよ。

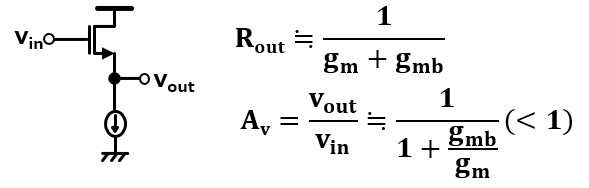

これもソースフォロワで例を取るのが適切な気がするけど、そのまま用いると基板バイアス効果によってgmbが出てくることから出力抵抗がその分だけ小さくなって、結果として小信号ゲインは1倍より小さな値となるんだね。

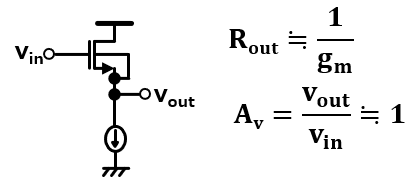

ただこれにボディ・ソース接続構造を用いると、gmbがなくなることで出力インピーダンスが大きくなって、小信号ゲインは1倍にすることができるんだね。

ソースフォロワの小信号等価回路での話は以下に述べてるので詳細はこっちを読んでみてね!

→ソースフォロワについて

スーパーソースフォロワについて

ちなみに余談だけど上記ソースフォロワの話題で、小信号と大信号の応答を混合しないように注意が必要だね。たまにソースフォロワの出力ノードの電位を予想する際に、入力ノードに小信号ゲインをかけて算出しようとする人がいるけど、そうではないよ。

出力はあくまで入力からVgs分ドロップした値となるよ(大信号応答)。ここでいう小信号ゲインってのは、入力をdc的なレベルから変動させた値(ac信号、小信号)に対して出力部の変動の感度ってことになるよ。

つまりは小信号ゲインが1倍であることは、Vin=Voutにさせてるわけではなくて、Vinを上下に変化させていってもVoutが常に等しくVgsだけシフトすることになるよ。まあ基板バイアス効果がある場合、出力ノードの変化に対してVgsが時々刻々と変化していき、結果として小信号ゲインに反映されてるわけだから、全く別の話ではないと思うんだけどね。

ボディ・ソース接続構造の欠点

デメリットはざっくりとは2つあると思ってて、一つはソースフォロワの記事でも挙げたように面積を喰うよ。

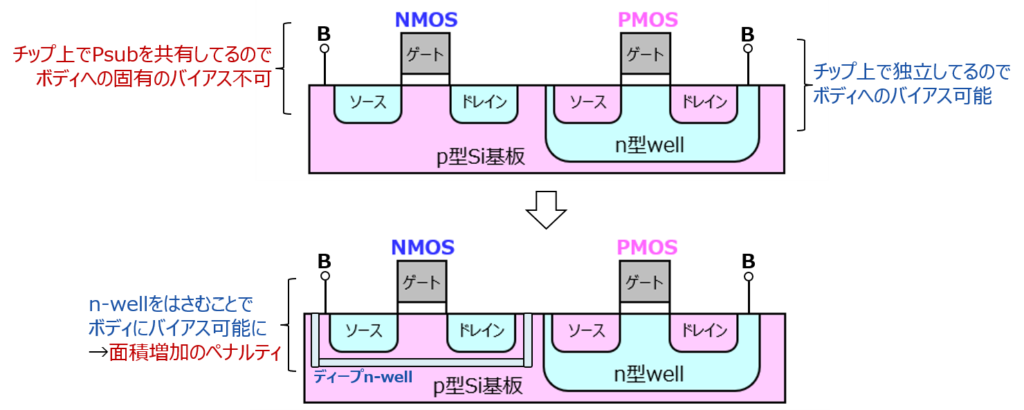

ここでpchの場合はもともと素子ごとに独立したn-wellを持っていることが多いから、その素子だけにボディバイアスを自由に変えられて問題はないんだけど、nchはp基板を共通して持っているためボディバイアスの自由度がないんだね。

なのでボディ端子をgnd以外につなげたい場合には以下のようにディープn-well構造にすることが必要で、これにすることでwellを追加して十分な幅を取る必要があることから、nch単体の面積が増加することになるよ。

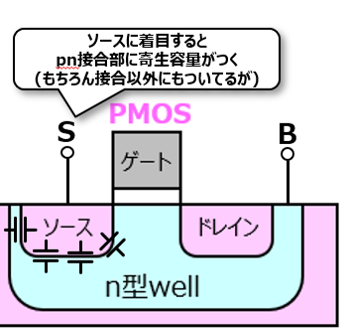

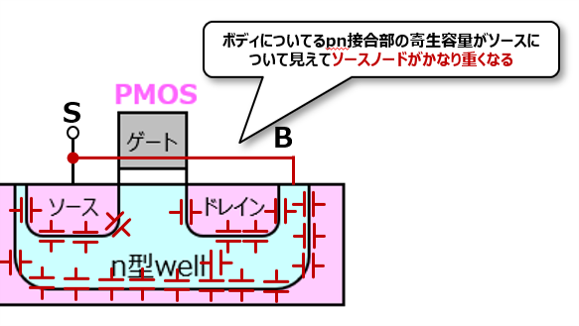

もう一つは、ソースにデバイス内の寄生容量がボディ分もつくことで、動作がかなり重くなることにあるよ。

イメージだけど、ボディに接続していなければデバイス単体でみてソースノードにつく寄生容量は以下の左のようになってるけど、

これがボディ・ソース接続構造にした場合にwell間の寄生容量もつくことになるんだね。このポンチ絵でも結構寄生容量が変わりそうってのは、明確なんじゃないかな。

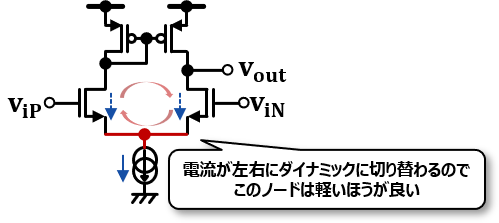

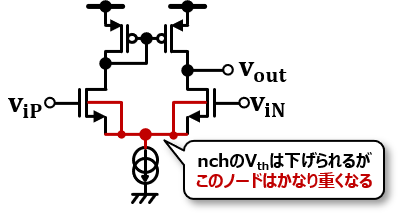

例えば以下のような差動対回路。差動対ってテール電流をそれぞれのnchが引き合うんだね。なので入力に応じて電流が右から左、左から右へと切り替わることで駆動させているんだね。

ところが低電圧化のために入力nchをボディ・ソース接続構造にすると、テール電流のノードが通常よりもかなり重くなって、電流の切り替えに時間がかかって動作速度が遅くなることが予想できるよね。

ボディってのはダイナミックに電位が動くことってほぼほぼないのかなって思うけど、ソースは上記のように変動があるケースは珍しくないので、ボディについてる寄生容量がつくのは見落とされがちなんだ。

デバイス起因の寄生容量ってのは設計者がなかなか介入しにくい点なので、デメリットをよく考慮した前提で設計しないといけないね。

今日はここまで、ほな。

雑談枠

ラーメンでも食べて、運命(健康診断)に抗うかぁ。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。