どうも、さわざわです。

今回はミスマッチについて触れていこうと思うよ。アナログ回路はいろいろなノイズが特性に大きく影響を与えてしまうことは言うまでもないんだけど、他にも閾値電圧であるVthや移動度などがプロセスによってばらついて、特性に影響が出るよ。なので設計段階でどれくらいばらつくかを考慮して、ばらついても特性として問題ないような設計が求められるんだ。その基礎理解として重要なので、みんなも勉強していってねい。

この記事を読めば閾値電圧ミスマッチについて基礎的な理解ができ、ミスマッチを減らす設計について理解できます。

ミスマッチとは?

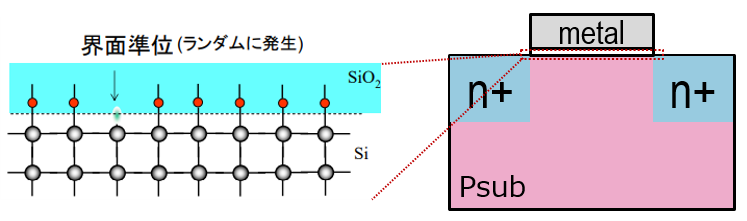

ここでいうミスマッチとは、MOSFET単体のVthやβが所望の値から若干ずれることをいうよ。これは不純物が揺らぐことで結果ときにVthがずれたり、酸化膜とチャネルの間の界面準位の発生によってβがずれるような理解で、原子レベルでの揺らぎが起因したものだってことだね。

詳細は後述するけど、非常に多くの原子の中からランダムに揺らぐより、数少ない原子の中からランダムに揺らいだほうが統計的にばらつきやすいので、微細プロセスのほうがばらつきは顕著だといえるよ。

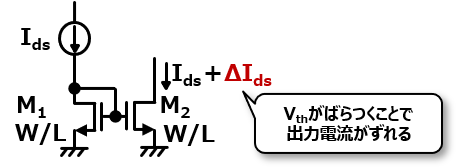

そしてVthやβがばらついてしまうと、以下のように理想的には同じ電流が出してほしいカレントミラーでも、ΔIdsが乗って所望の電流からずれてしまうんだね。以降はVthミスマッチに着目して触れていこうと思うよ。(βに関しても結論は大きく変わらないかな。)

ミスマッチに効くパラメータ

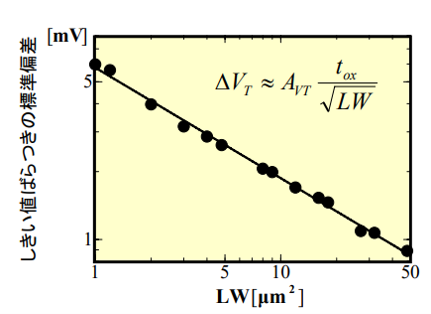

Vthばらつきをの標準偏差示すσ(Vth)は以下のような式で表せるよ。ここからわかるようにσ(Vth)は以下のように√LWに比例して小さくなることになるね。ここでAvtってのはばらつきの係数のようなもので、これはプロセスによって決まるものだよ。

ちなみに余談(割と重要な余談)だけど、微細プロセスを用いる場合にはサイズを大きくしていくと、ある点で物理的に距離が離れていってミスマッチがむしろ悪化する傾向ってのがあるので、注意が必要だよ。(どのファウンドリでもそうなのかは自信がないのであまり深ぼらないでおくね。)

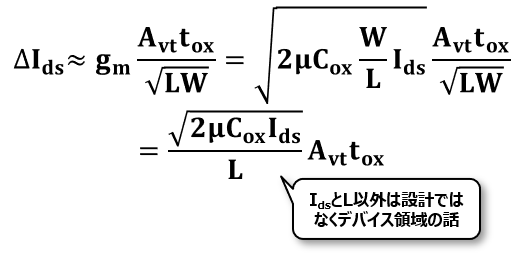

んでVthがばらついた際にMOSFETのどこに効いてくるかというと、当然Vgsに対してVeffの見え方が変わってくるよね。なので電流としてはVthのばらつきにgmがかかって以下のように表せることがわかるかな。

この式をもとにどうすればミスマッチを減らすことができるかを次項から深ぼって考えていこう。

より詳細な内容は以下でも勉強してみてね。

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

Analog Integrated Circuit Design

設計観点でミスマッチをどう減らしていくか

σ(Vth)の場合はWとLを増やしていけば、ばらつきを減らせることが明確であったよね。ところがΔIdsで見た場合にgmがかかってくるので、電流源のnchだけを考慮しても単純にサイズを大きくするって議論ではなくなってくるよ。

どういうことかっていうとWを大きくしてσ(Vth)を√Wだけ小さくしたとしても、gmが同じく√Wだけ大きくなってしまうので小さな揺らぎを大きく電流として見せてしまい、結果としてΔIdsは変わらないっていえるんだね。(後述するけど、Wを大きくして所望の電流を増やすのであれば、ばらつきは小さく見せられる)

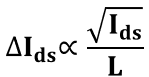

ではΔIdsの式を変形していくと、以下のようにgm内部のWが確かに打ち消しあって、残りがこうなるね。ここで回路設計者が自由にいじれるパラメータはIdsとLだけだよね。

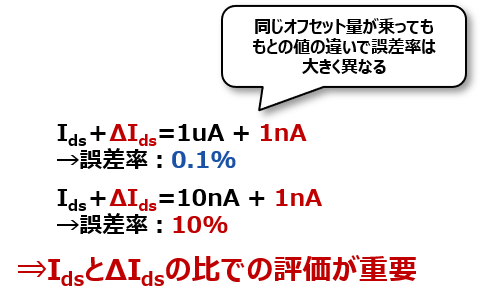

ここでもう一つ重要なことがあって、ΔIdsを小さくすることは非常に大事なんだけど、これだけで評価しても意味ないんだね。これはノイズの話と一緒で、オリジナルの値に対して相対的にどれくらい影響があるかを評価することで意味のある指標となるんだ。

つまりは電流がわずかにしかばらつかなくても、そもそも非常に定電流動作をするのであれば、結果としてミスマッチは大きく見えてしまうってことだね。

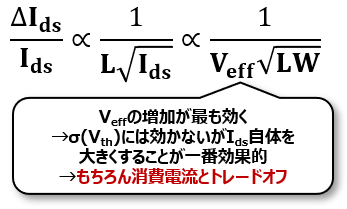

なのでIdsとΔIdsの比として議論すると、以下のようになるね。ここでもしIdsは他の特性や仕様により等しい値で決まっていた場合や入力デバイスのように自分でIdsを決めていない場合には、Lを大きくしてミスマッチを下げる他なくなるね(電流は変化しないようにVeffやWで調整要)。ここでLを上げてミスマッチを減らすと動作レンジが狭まることに注意が必要だね。

あるいは電流源において電流を大きくしてミスマッチを上げることも辞さないって場合は、以下のようにIdsをさらに分解して、最初のσ(Vth)と同様に√WLを大きくすることか、Veffを上げることが効果的となるんだね。

ここでVeffはσ(Vth)には効かないわけだけど、最終的には電流を増やすことで一番効果的にミスマッチ減に効くパラメータってことだね。ただミスマッチ減に定電流が増えるって結構なペナルティな気がするね。

ちなみにVthのミスマッチを減らす手法について述べてきたけど、実際にはβも√WLを大きくすることでばらつきを小さくできることには変わりないよ。

そしてそれらを含めて、モンテカルロシミュレーションでデバイスのばらつきを考慮しても問題なく所望の特性を出せる設計をすることが設計者には求められるんだね。

デバイス単体の能力として以下も読んでみてねん。

→固有利得について_dcゲイン調整と周波数応答

今日はここまで、ほな。

雑談枠

毎朝日焼け止め塗れるの偉すぎわろた。偉すぎて申し訳ないって感じ。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。