どうも、さわざわです。

今回からオペアンプにおける安定化設計について触れていこうと思うよ。前回はローパスフィルタを用いた簡易的なモデルでポールと安定性の関係について述べてきたけど、今回はそれをオペアンプの内容に落としていこうと思うよ。また、安定化設計において重要な位相余裕(PM)に伴う回路特性について触れて、位相補償の内容につなげていこうと思うよ。実用的な内容なので、みんなも勉強していってねい。

この記事を読めば、オペアンプにおける安定化設計における不安定なケースについて学べ、位相余裕に対する回路特性の違いがわかります。最適な位相余裕を解析するために、ナイキスト線図での位相とゲインの考慮を含めてクローズドループの伝達関数の議論をします。

ネガティブフィードバックと安定性の復習

まず前回までの復習だけど、ネガティブフィードバックを入れると利点がたくさんある一方で、安定性が悪化しないように設計しないといけなかったんだったね。

→ネガティブフィードバックについて

安定性設計におけるポールと位相余裕について

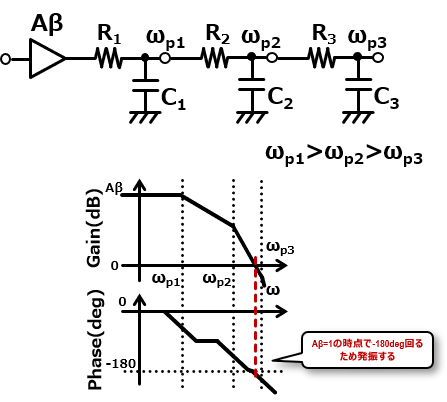

どういうケースで不安定になるかというと、低周波から高周波応答に遷移していく中で、ポールωpを迎えるたびにゲインは-20dB/decのペースで下がっていき、10ωpの段階で位相が-90degずれるんだったね。そしてAβの信号が、位相が-180deg回った時点でゲインを1倍以上持っていたら、↑のようにフィードバック信号がもとに信号にどんどん加算されていく応答になることから、発振することになるんだったね。

1段オペアンプの安定性について

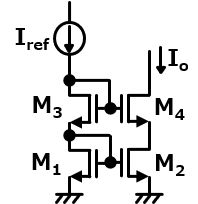

安定化はAβが大きいほど不安定になりやすいので、オペアンプにおける安定化のワーストケースは以下のようなβ=1のユニティゲインバッファだといえるよ。これはアンプのゲインが大きいほど入力電圧をそのまま出力してくれる回路になるよ。

じゃあオペアンプの中身が1段構成の場合を考えよう。

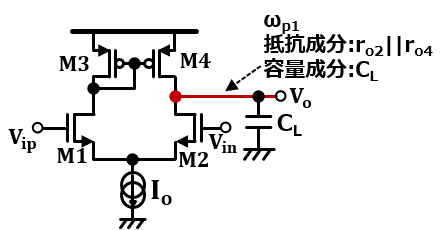

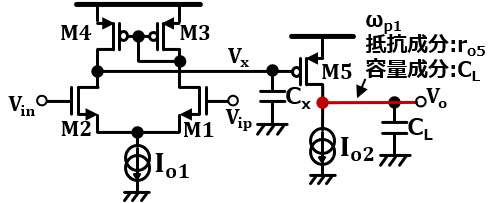

この際のポールがどこになるかというと、まず出力ノードに大きな負荷容量CLがついているよ。これは次段のゲート容量とかを含めた大きな値と想定して、加えてこのノードにはオープンループで出力抵抗にro2//ro4とかなり大きな値となるよ。なのでこのオペアンプの中で、出力ノードだけとびぬけて大きな値のRCがかかることになり、ポール周波数として小さく支配的(ゲイン減衰が始まる最低周波数)といえるよ。

その次にはいろいろ考えられるけど、例えばpchのゲートに当たるアクティブカレントミラー部分とか。ゲート容量とかいろいろつくと思うけど、仮に容量はそれなりにかかったとしても、抵抗成分としてはダイオード接続によって1/gmがつくってレベルだよね。つまりポール周波数としては、さっきのものと比べてかなり大きなといえる。

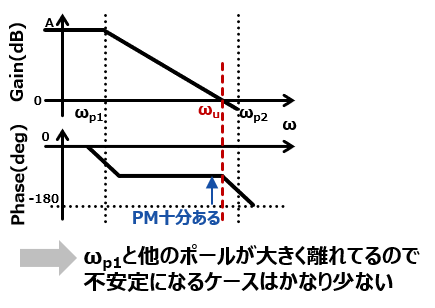

グラフとしてみると以下のようなケースが多いといえて、最初のポールを迎えてから次のポールを迎えるまで非常に周波数として離れていることから、位相が-180deg回るころにはゲインが1倍になるユニティゲイン周波数ωuをとっくに迎えているといえるね。つまり不安定になるケースはほぼないといえるよ。

2段オペアンプの安定性について

じゃあこれが2段構造のオペアンプになるとどうなるか考えていこう。

ポールとして支配的なとこを上から挙げてくと、まずωp1が以下。

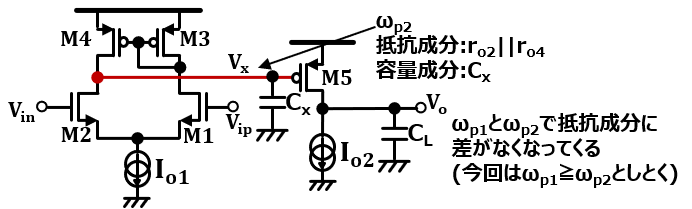

次にωp2。

ここで最も重要な点は、かなりポール周波数の小さい点が2つに増えたことになるよ。つまり、1段目が単純なシングルエンドの場合、ωp1とωp2は抵抗的にはroが見えてどちらもかなり大きな値、容量でみるとCLのほうが大きな値になるとωp1のほうが小さくなるのかなって感じ(ゲイン段として1段目をカスコードとかにすると出力抵抗の差でωp2のほうが小さくなるのでここはケースバイケースのような)。

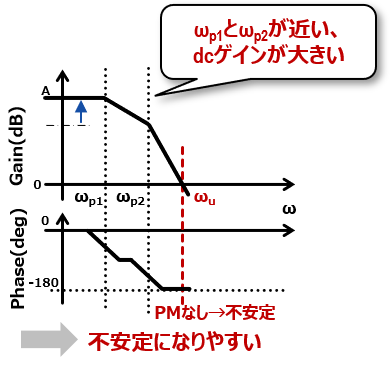

いずれにしてもここで重要なのはωp1とωp2が比較的近い値になりうるってことになるね。そうすると以下のように、ゲインが下がり始めた段階で直ちに-180deg回るようなケースってのが想定されて、ほぼほぼ不安定になってしまうといえるよ。

そして簡単に予想ができるかもだけど、当然ソース接地回路を2段目に置いた2段オペアンプであれば、かなりdcゲインが大きいことになるよね。要はゲインが落ち始めて1倍に到達するまでにかなり高周波まで行かないといけないことになるから、ポールの位置と合わせて不安定になりやすい要素といえるんだね。

先に次回以降触れる位相補償の話に入ると、位相補償は簡単に言うといまいま近くにいるωp1とωp2を遠ざけて、低周波の段階からωp1でゲインを落としていき、ωp2を迎えて-180deg回るまでにゲインを1倍まで落としていく手法になるよ。まあ要は動作速度を落として安定性を取るって、以前に挙げたような話だね。まあこれは次回以降。

ここでは回路を安定化するってどういうことか。前回位相余裕(PM)って概念を説明したけど、上記の2段オペアンプの例とかは位相余裕がほぼない(0deg以下)ような例なんだよね。じゃあこれがどれくらいPMがあればいいのか、位相補償での指標にもなるのでここを次項で触れていこう。

PMの最適値

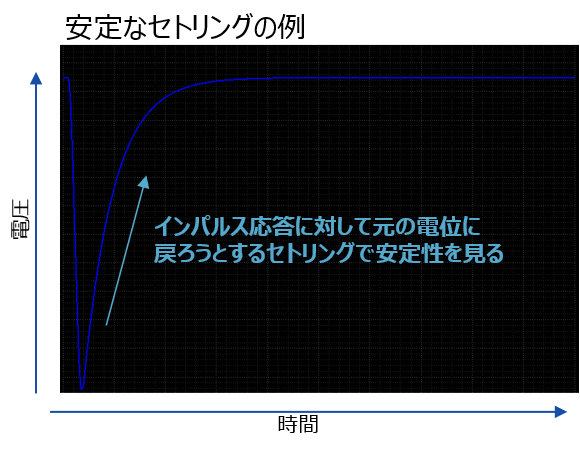

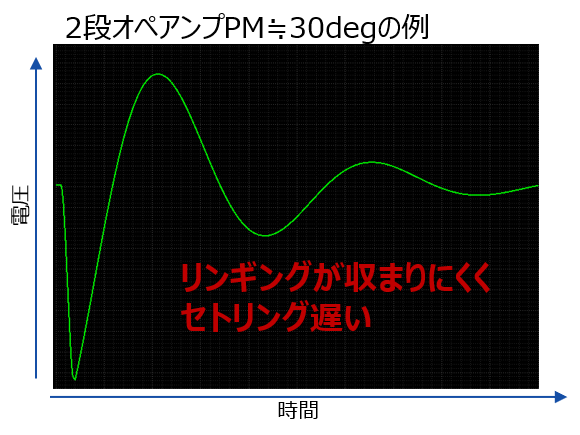

上記のようにPMが0deg以下だったとすると、外部からインパルス応答を与えた際にユニティゲインバッファはもとの応答まで戻ろうと駆動してくれるはずが、以下のように発振するんだね。これを次回以降述べるような位相補償なり回路パラメータの最適化なりで、PMを持っていくとどのようにセトリングが変化するかを見ていこう。

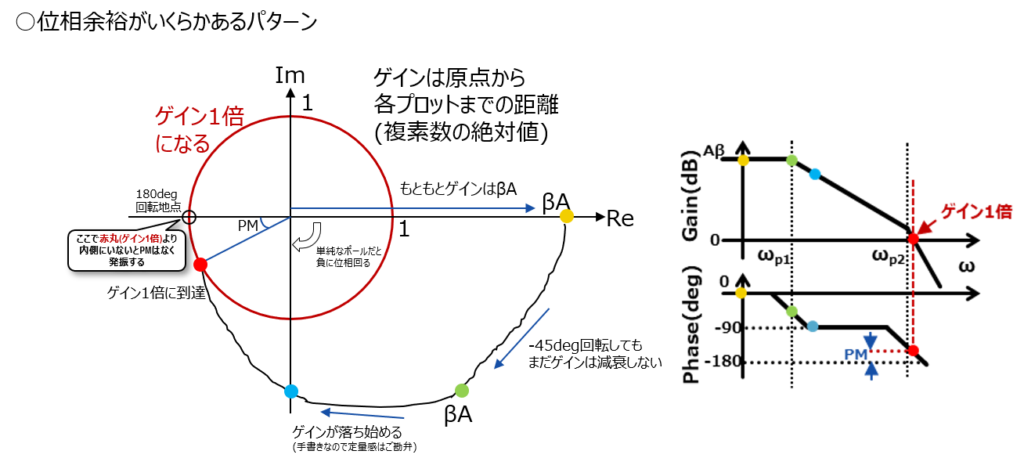

そもそものゲインと位相の関係をちゃんと読み解くには、以下の左のようにナイキスト線図で考えることが必要になってくるよ。

ナイキスト線図は右のボード線図(Gain, Phaseの周波数応答)を別の書き方をしたようなものに過ぎないんだけど、ナイキスト線図上は複素平面で描かれていてその絶対値である原点からの距離がゲインとなるよ。

つまりスタートは位相が全く回転していないとして、x軸上にβAのゲインを持つことになってるよ(黄●)。

ここで最初のポールが近づき位相が回転し始めると、最初の地点から反時計回りに動き出して緑●へと動くよ。ちなみに-45deg回転した時点でようやく最初のポールの周波数にたどり着いたといえるので、ここではまだゲインはほぼ減衰しないはずだよ。

そこから-90degまで位相が回転すると、-45deg→-90degにかけてゲインがどんどん減衰を始めるよ(青●)。そしてゲインが1倍になる地点が赤●。この時点で位相はスタートから-180deg回転していないよね。つまりPMがあることになる。

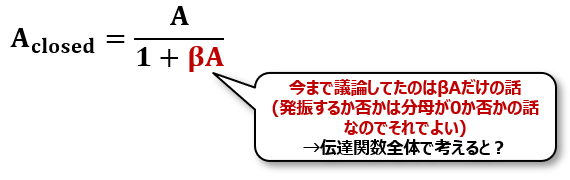

じゃあここからはそのPMがいくらか必要かって話をしたいんだけど、その前にまだ話さなきゃいけないことがあるんだ。今までの議論はβAだけの話だったよね。

これは前回から、NFB込みのクローズドループの伝達関数において、βAが実数で-1になった際にゲインが無限となって発振するって話からきてたよ。なので発振するか否かだけの議論であればそれでよかったんだけど、安定ですの後に考えるのは実際のクローズドループの伝達関数だよね。

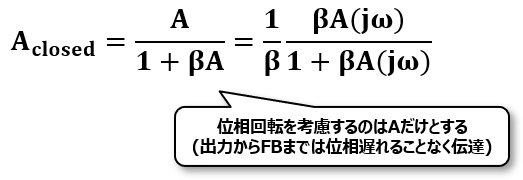

ここで位相遅れなど周波数応答の考慮が必要なのは上記伝達関数内のAだけだとして複素数A(jω)とでも書こうか。そうすると今までのβAの議論をできるだけ活かしたいので、以下のように式変形をして考えよう。

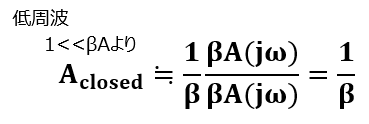

じゃあこの際に低周波の領域であれば、先のナイキスト線図からもわかると思うけどβAは1よりはるかに大きい値を持っていることになるので、以下のようにかけるね。

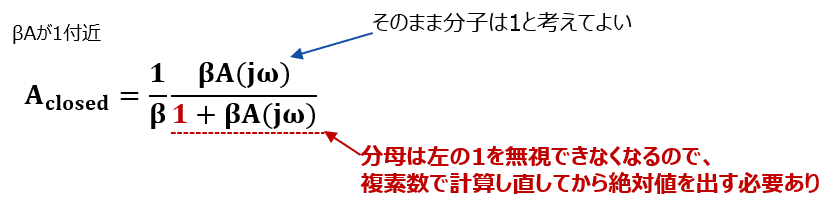

一方でβA=1の付近になってくると、低周波で無視した以下の1をちゃんと考慮しなくちゃいけなくなるね。つまりは分子はそのままβA(jω)=1を入れればいいのに対して、分母は複素数βA(jω)に対して実数1を加算してから、絶対値を計算する必要が出てくるよ。

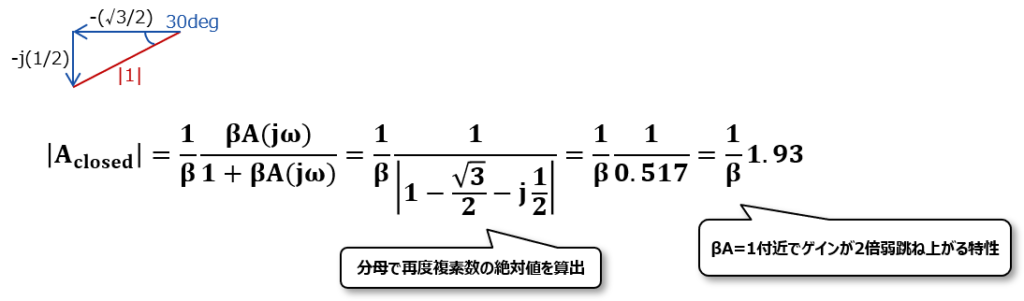

ここでようやくPMの話の戻るよ。じゃあ以下のようにPM=30degだったとしよう。

その際の絶対値が1であるβAを複素数に分けると、βA(jω)=-(√3/2)-j(1/2)といえるね。なので伝達関数の計算は以下のようになるね。

この際もともと1/βであったゲインが、βA=1に近づいたときに一気に2倍弱まで跳ね上がる特性となるんだね。その結果発振はしないものの、所望のセトリングに瞬間的にゲインが大きくかかって見えて、以下のようにリンギングするセトリングを持つことが考えられて、結果としてセトリング時間は悪化することになるよ。

ここまで来たら後は汎用的に数ケース見ればおのずと答えが出てくると思うけど、PMが90degの場合は、以下のようにゲインが下がりやすい特性っていえるね。これでリンギング自体は避けられるけど、かなり遅いセトリングになってしまうよ。

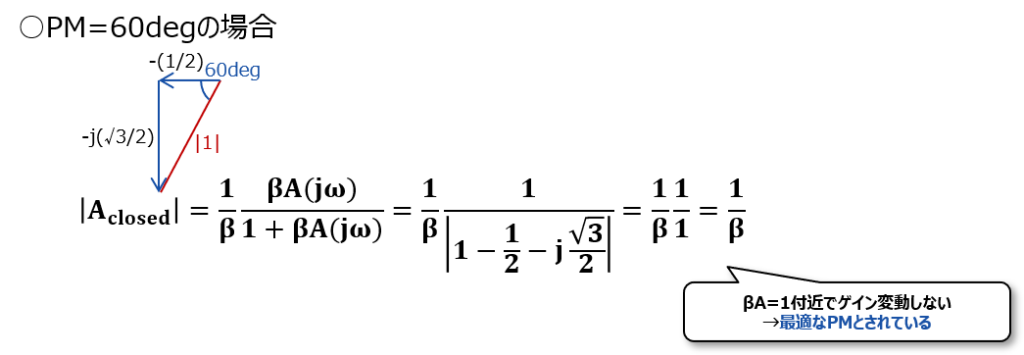

PM=60degでは以下のように1/βちょうどになることから、急にゲインが変動して良くないセトリング特性を持つことが少なく、PMとして60degが最適とうたわれることが多いよ。

今回の内容は以下あたりを読めば十分な理解ができると思うのでおすすめだよ。

Analog Integrated Circuit Design

次回予告

じゃあ位相補償の話に入って、どうやって2段オペアンプを用いたユニティゲインバッファでPM=60degを達成できるかを次回から考えていこう。

結論から言うと以前に挙げたように第1ポールと第2ポールを離すってことになると思うんだけど、ポールスプリットとか単に回路パラメータを調整するとか、回路プロパティによっても補償の難易度が変わってくると思うのでかなり回を重ねて深ぼって説明していこうと思うよ。

次回→オペアンプの位相補償:ポールスプリットについて-基礎概念を理解しよう編-

今日はここまで、ほな。

雑談枠

回転ずしのから揚げがなんか好き。特別おいしいってわけではないのかもだけど、寿司を少しつまんだ後に食べると格別においしいような。高いけど。味も価格も屋台バイアスなのかもね。

おすすめ書籍紹介(Amazonに飛びます)

アナログCMOS集積回路の設計 (基礎編)

(最近第2版が出て原版のupdateが反映された感じ)

アナログCMOS集積回路の設計 (応用編)

(最近第2版が出て原版のupdateが反映された感じ、以下のソフトカバーと比較すると高い気が。。)

Design Of Analog Cmos Integrated Circuit , 2Nd Edition

(↑の原版のIndian版(英語)で2ndからは訳書にない新内容有り、ペーパーバックは安め。英語に抵抗ない方はこっち買うほうが内容的にも値段的にもお得)

Analog Integrated Circuit Design

(網羅的かつ設計観点で深めに学べる印象なのにわかりやすく書いてて初級向け、演習も易しめで取っつきやすい。ただハードカバーのため高い、、)

CMOSアナログ回路入門: LSI設計者のための (半導体シリーズ)

(初学者向け。実用的な内容もあるがあまり深ぼらないので、あくまで勉強するきっかけを作る本な気が。)

Xアカウント

https://x.com/swzw6112

–お問い合わせ–

以下よりお願いします。